TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-48 V2.0, 2007-07

CPU, V2.0

2.7.2 Load-Store Pipeline Instructions

2.7.2.1 Address Arithmetic Timing

Each instruction is single issued.

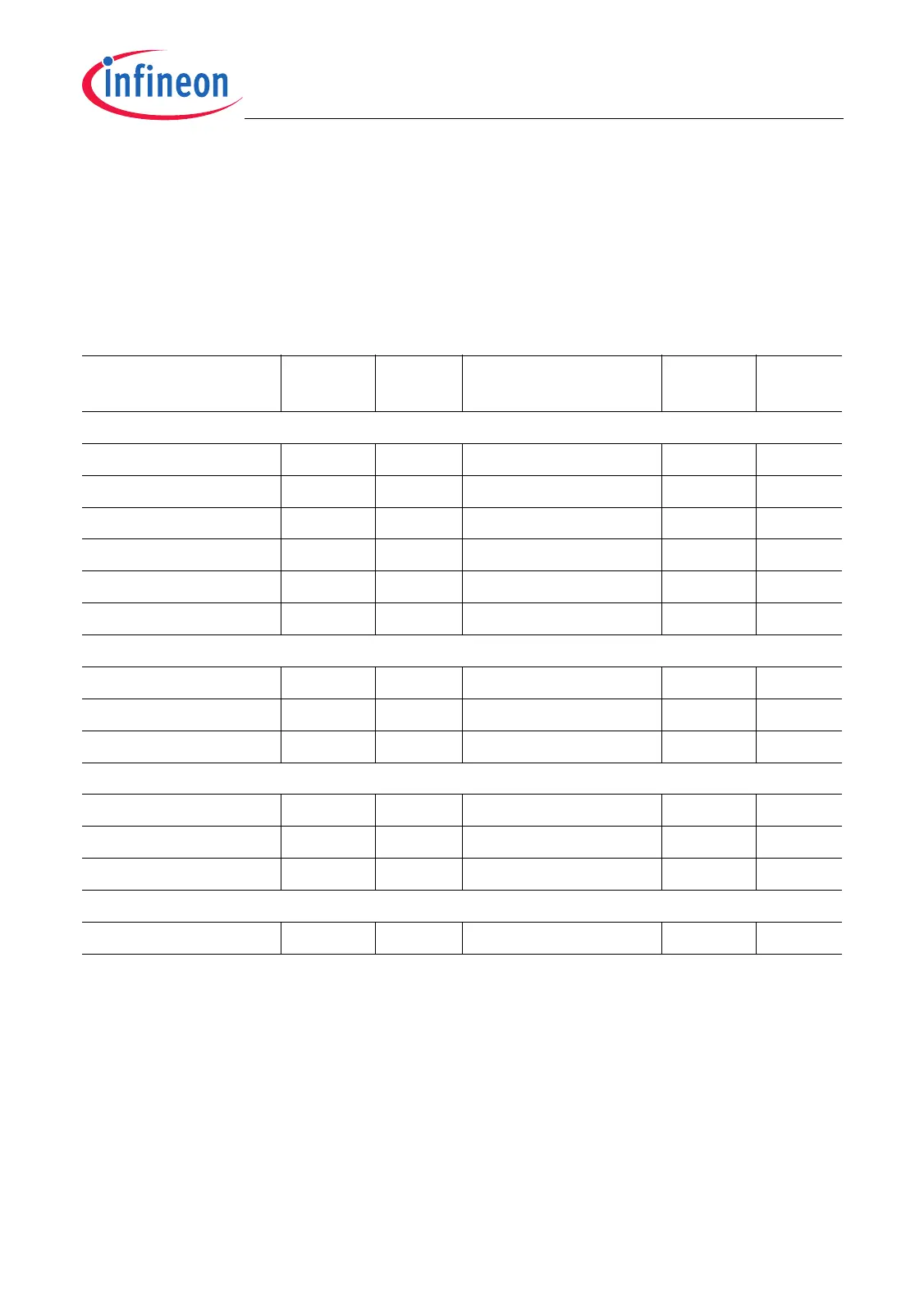

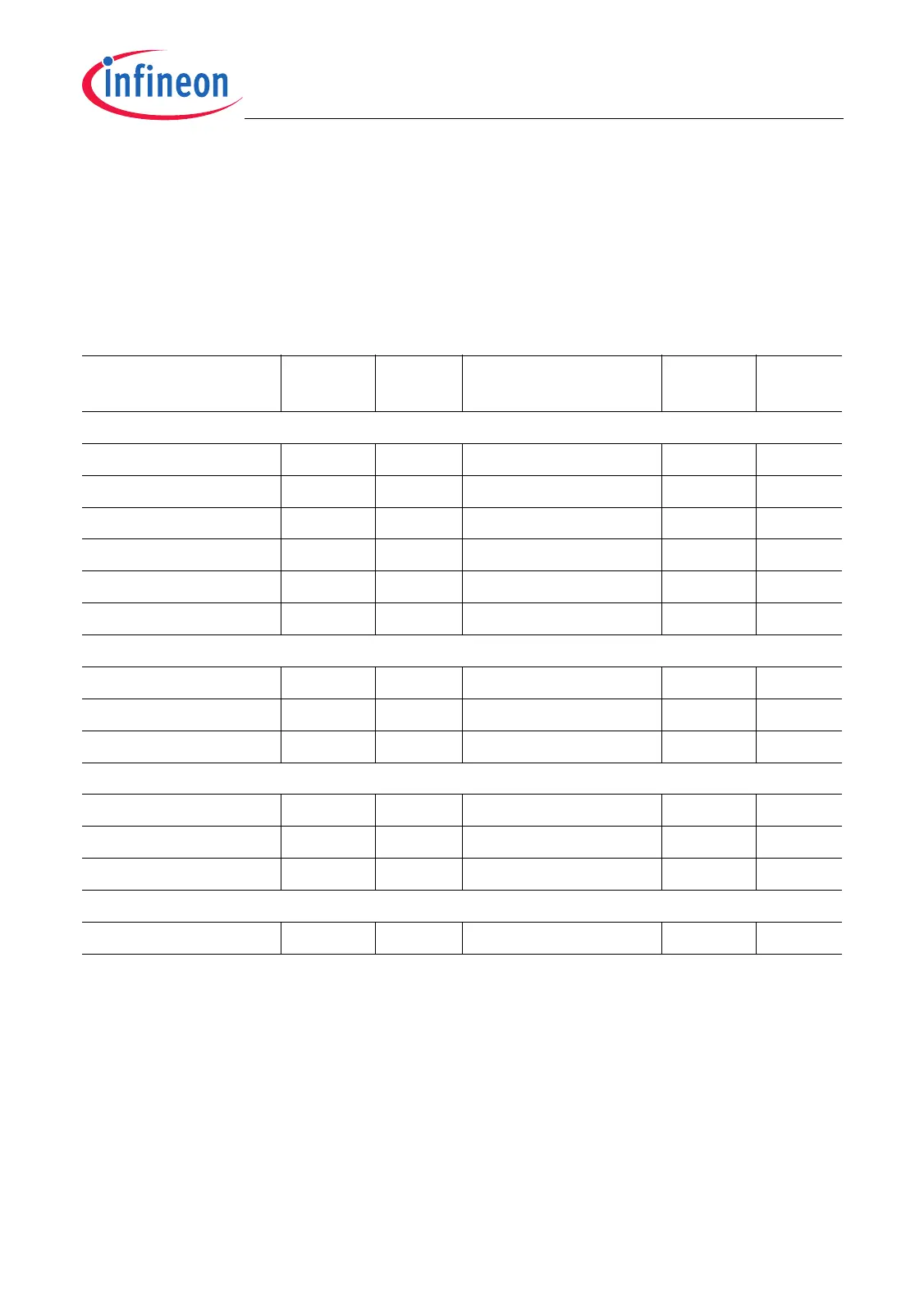

Table 2-14 Address Arithmetic Instruction Timing

Instruction Result

Latency

Repeat

Rate

Instruction Result

Latency

Repeat

Rate

LS Arithmetic Instructions

ADD.A 11GE.A 11

ADDIH.A 11LT.A 11

ADDSC.A 11NE.A 11

ADDSC.AT 11NEZ.A 11

EQ.A 11SUB.A 11

EQZ.A 11NOP 11

Trap and Interrupt Instructions

DEBUG –1TRAPSV

1)

1) Execution cycles when no TRAP is taken. The execution timing in the case of raising these TRAPs is the same

as other TRAPs such as SYSCALL.

–1

DISABLE –1TRAPV

3)

–1

ENABLE –1RSTV –1

Move Instructions

MFCR 11MOV.A 11

MTCR –1MOV.AA 11

MOVH.A 11MOV.D 11

Sync Instructions

DSYNC

2)

2) Repeat rate assumes that no shadow register write-back is pending, other wise the repeat rate will depend

upon the time for all delayed memory operation to occur.

–1ISYNC

3)

3) Repeat rate assumes that code refetch takes a single cycle.

–1

Loading...

Loading...