TC1796

System Units (Vol. 1 of 2)

Direct Memory Access Controller

User’s Manual 12-92 V2.0, 2007-07

DMA, V2.0

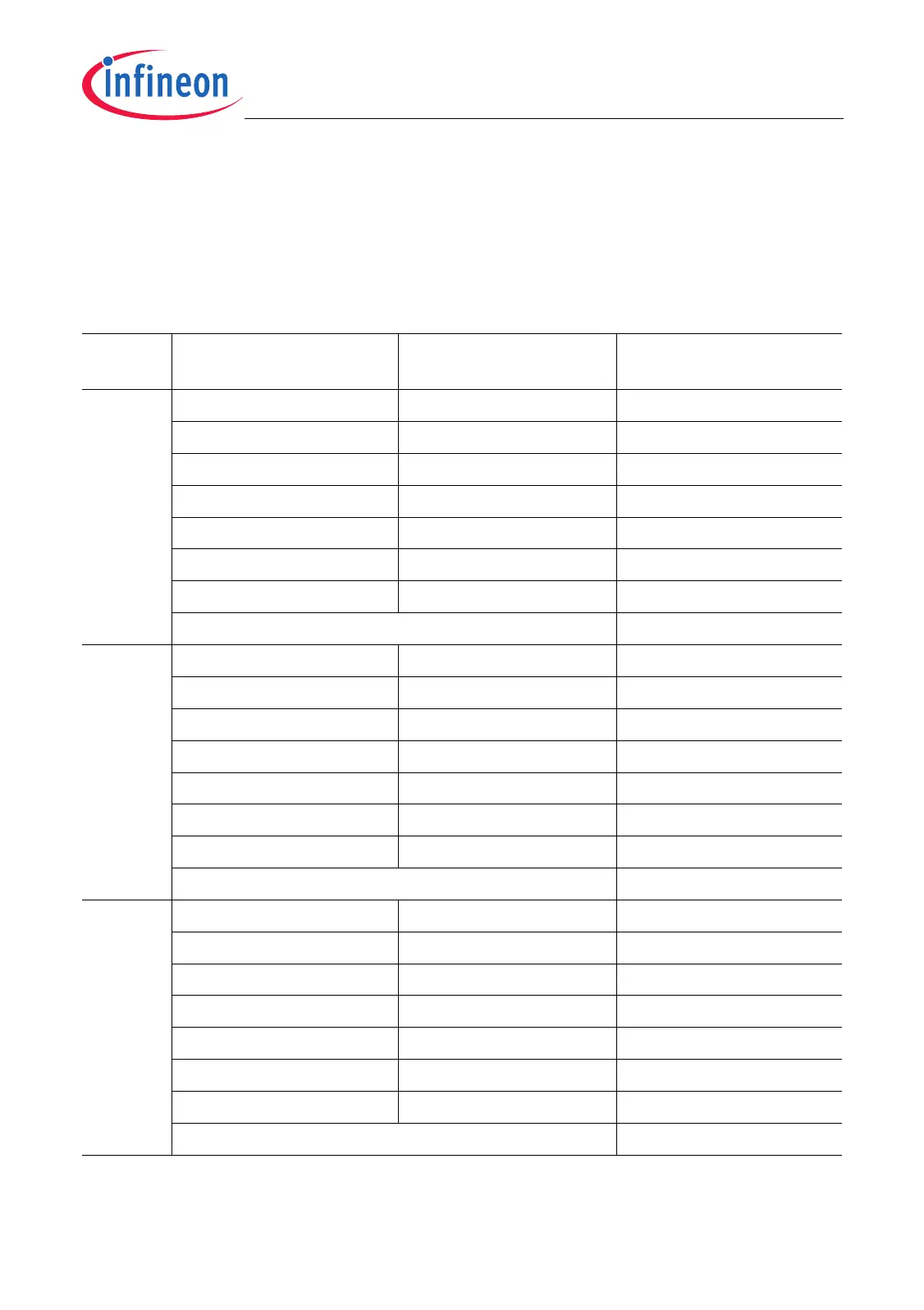

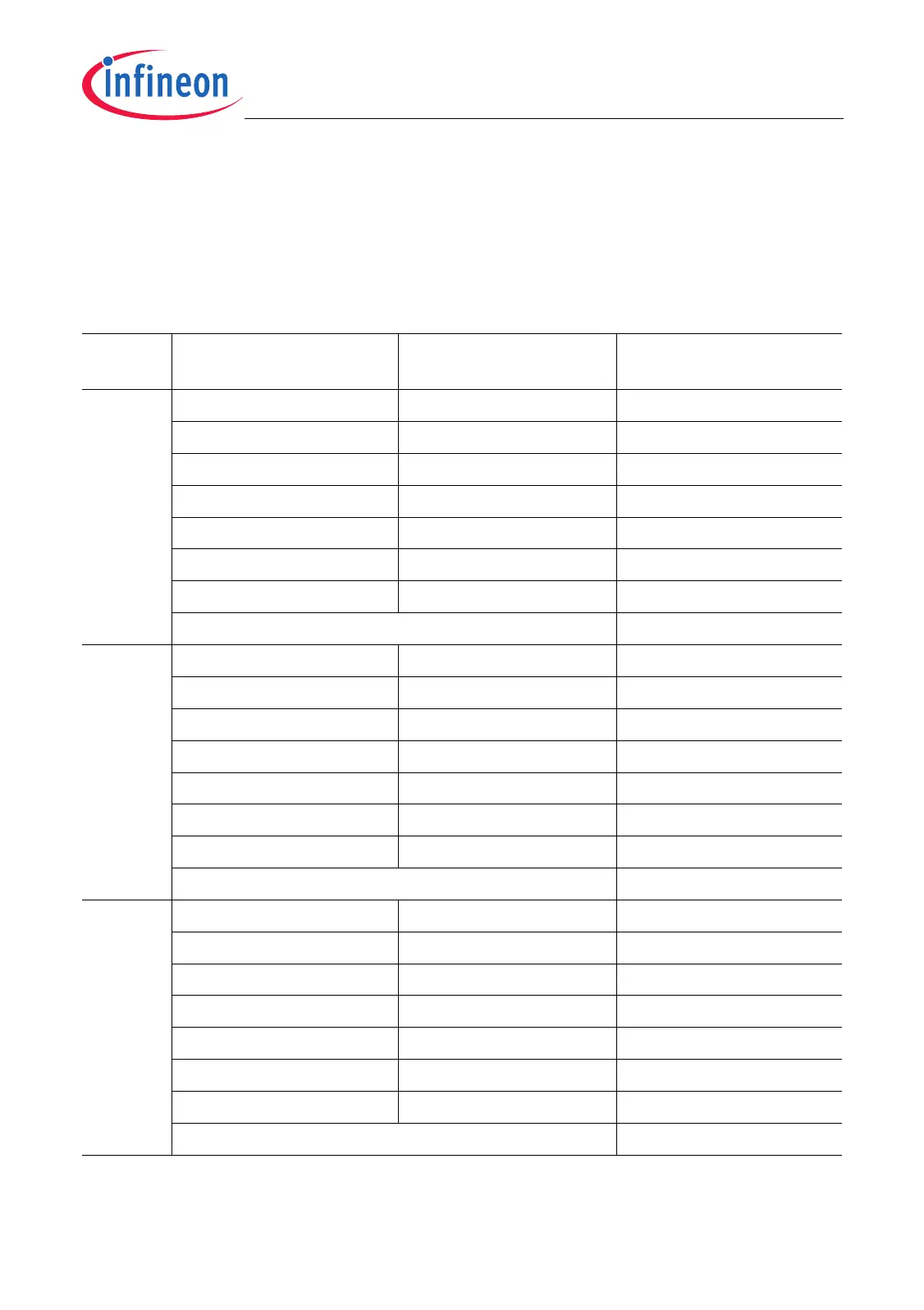

12.3.1 DMA Request Wiring Matrix

The DMA request input lines of each DMA channel within DMA Sub-Block 0 and 1 are

connected to request output lines from the peripheral modules according Table 12-9 and

Table 12-10.

Table 12-9 DMA Request Assignment for DMA Sub-Block 0

DMA

Channel

DMA Request Line DMA Requesting Unit Selected by

00 CH17_OUT DMA channel 17 CHCR00.PRSEL = 000

B

SCU_REQ0 Ext. Request Unit

1)

CHCR00.PRSEL = 001

B

TIR SSC0 CHCR00.PRSEL = 010

B

RIR SSC0 CHCR00.PRSEL = 011

B

TIR SSC1 CHCR00.PRSEL = 100

B

SR4 MLI0 CHCR00.PRSEL = 101

B

SR4 MLI1 CHCR00.PRSEL = 110

B

not connected (0) CHCR00.PRSEL = 111

B

01 CH00_OUT DMA channel 00 CHCR01.PRSEL = 000

B

SCU_REQ1 Ext. Request Unit

1)

CHCR01.PRSEL = 001

B

TIR SSC1 CHCR01.PRSEL = 010

B

RIR SSC1 CHCR01.PRSEL = 011

B

TIR SSC0 CHCR01.PRSEL = 100

B

SR5 MLI0 CHCR01.PRSEL = 101

B

SR5 MLI1 CHCR01.PRSEL = 110

B

not connected (0) CHCR01.PRSEL = 111

B

02 CH01_OUT DMA channel 01 CHCR02.PRSEL = 000

B

SCU_REQ2 Ext. Request Unit

1)

CHCR02.PRSEL = 001

B

SR4 ADC0 CHCR02.PRSEL = 010

B

SR4 ADC1 CHCR02.PRSEL = 011

B

SR4 MLI0 CHCR02.PRSEL = 100

B

SR4 MLI1 CHCR02.PRSEL = 101

B

TIR SSC0 CHCR02.PRSEL = 110

B

not connected (0) CHCR02.PRSEL = 111

B

Loading...

Loading...