TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-159 V2.0, 2007-07

GPTA, V2.0

24.3.3 Phase Discriminator Registers

GPTA0_PDLCTR

GPTA0 Phase Discrimination Logic Control Register

(078

H

) Reset Value: 0000 0000

H

GPTA1_PDLCTR

GPTA1 Phase Discrimination Logic Control Register

(078

H

) Reset Value: 0000 0000

H

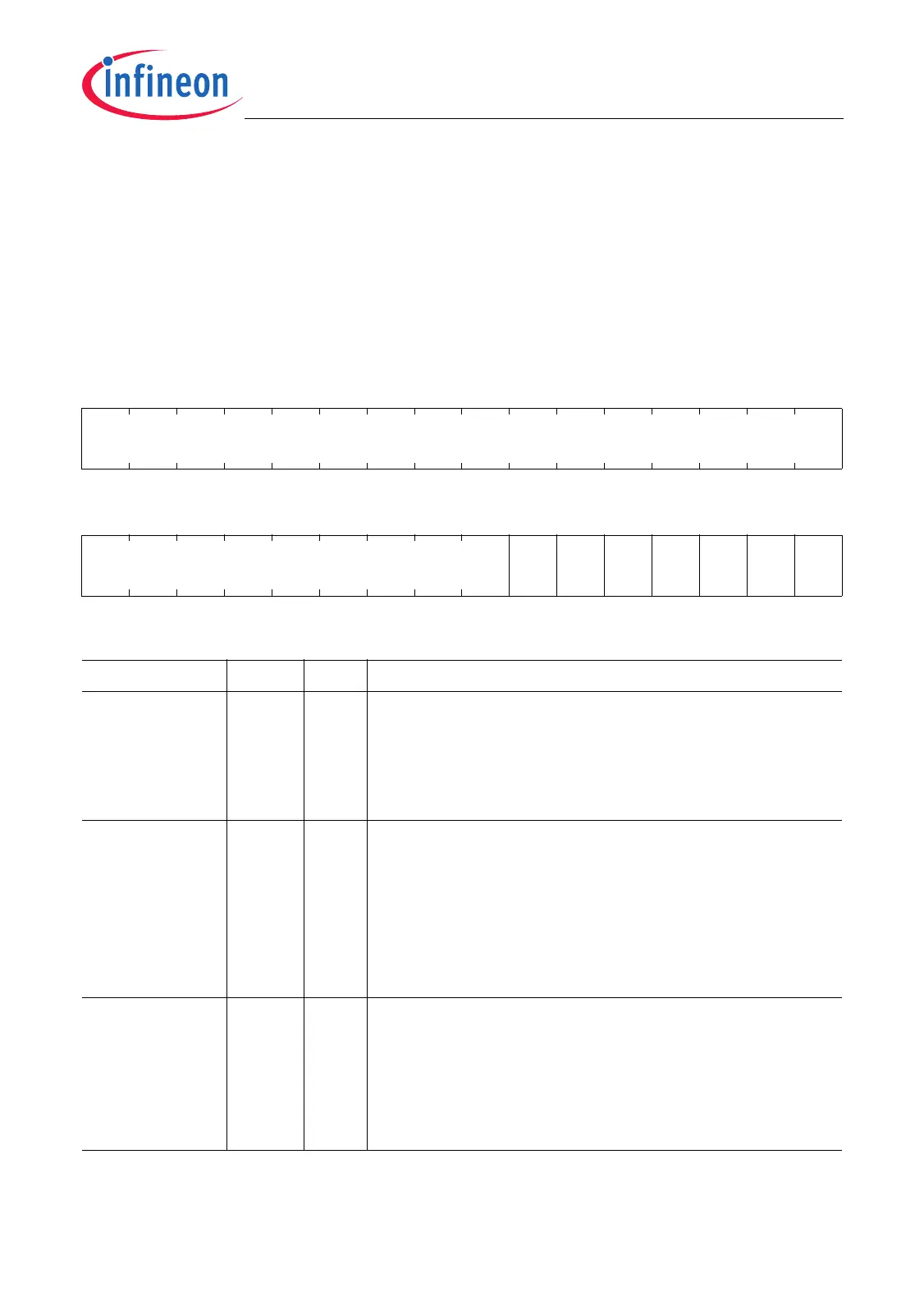

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0

ERR

1

TSE

1

MUX

1

0

ERR

0

TSE

0

MUX

0

r rwh rw rw r rwh rw rw

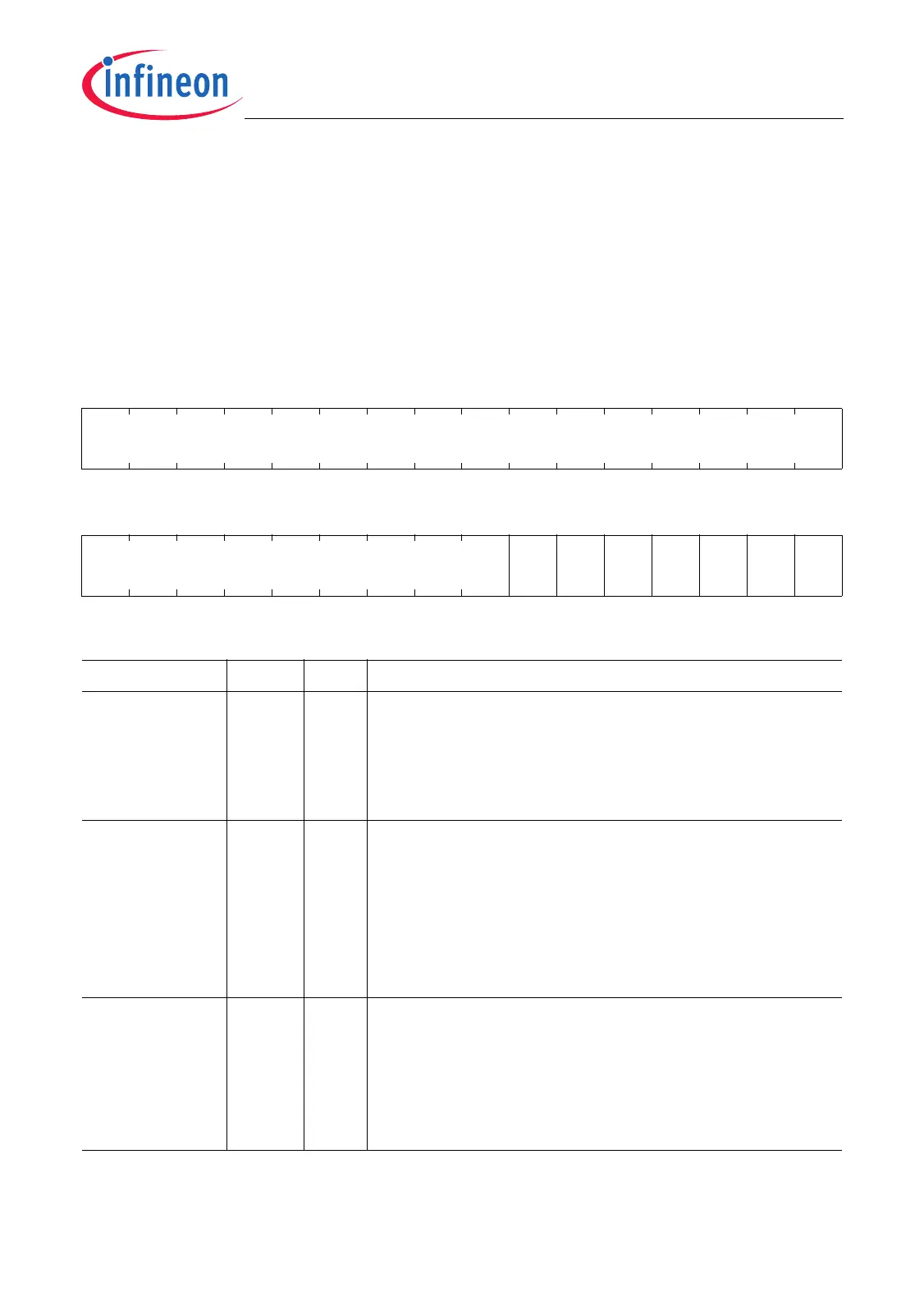

Field Bits Type Description

MUX0 0rwOutput Signal Source Selection for PDL0

0

B

DCM0 cell input is driven by fed-through FPC0

output lines

1

B

DCM0 cell input is provided with PDL0

“Forward” and “Backward” pulses

TSE0 1rw3-Sensor Mode Enable for PDL0

0

B

PDL0 operates in “2-Sensor Mode” and DCM1

cell input is driven by fed-through FPC2 output

lines

1

B

PDL0 operates in “3-Sensor Mode” and DCM1

cell input is provided with PDL0 error

information

ERR0 2rwhError Flag for PDL0

0

B

No error has occurred

1

B

Error detected in “3-Sensor Mode”: all PDL0

input signals are simultaneously provided with

high or low level

Bit ERR0 is bit protected (see Page 24-155).

Loading...

Loading...