TC1796

System Units (Vol. 1 of 2)

On-Chip System Buses and Bus Bridges

User’s Manual 6-22 V2.0, 2007-07

Buses, V2.0

6.4.4 Address Alignment Rules

FPI Bus address generation is compliant with the following rules:

• Half-word transactions must have a half-word aligned address (A0 = 0). Half-word

accesses on byte lanes 1 and 2 addresses are illegal.

• Word transactions must always have word-aligned addresses (A[1:0] = 00

B

).

• Block transactions must always have block-type aligned addresses.

6.4.5 FPI Bus Basic Operations

This section describes some basic transactions on the FPI Bus.

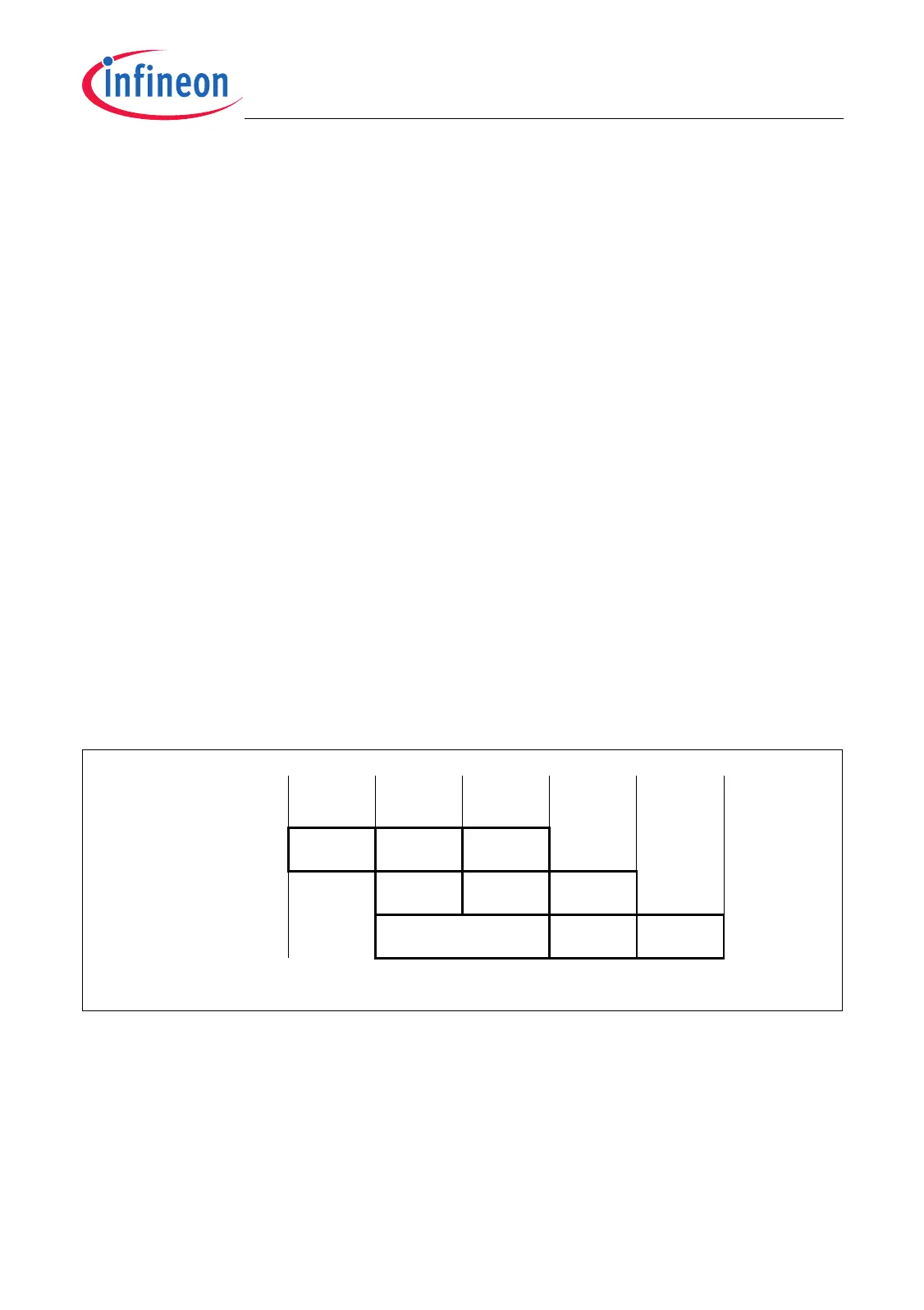

The example in Figure 6-7 shows the three cycles of an FPI Bus operation:

1. Request/Grant Cycle: The FPI Bus master attempts to perform a read or write

transfer and requests for the FPI Bus. If the FPI Bus is available, it is granted in the

same cycle by the FPI Bus controller.

2. Address Cycle: After the request/grant cycle, the master puts the address on the

FPI Bus, and all FPI Bus slave devices check whether they are addressed for the

following data cycle.

3. Data Cycle: In the data cycle, either the master puts write data on the FPI Bus which

is read by the FPI Bus slave (write cycle) or vice versa (read cycle).

Transfers 2 and 3 show the conflict when two masters try to use the FPI Bus and how

the conflict is solved. In the example, the FPI Bus master of transfer 2 has a higher

priority than the FPI Bus master of transfer 3.

Figure 6-7 Basic FPI Bus Transactions

At a block transfer, the address cycle of a second transfer is extended until the data

cycles of the block transfer are finished. In the example of Figure 6-8, transfer 1 is a

block transfer, while transfer 2 is a single transfer.

Request /

Grant

Data

Cycle

Address

Cycle

Bus Cycle 1 2 3 4

Request /

Grant

Address

Cycle

Data

Cycle

Data

Cycle

Address

Cycle

Request /Grant

5

MCA05634_mod

Transfer 1

Transfer 2

Transfer 3

Loading...

Loading...