TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-251 V2.0, 2007-07

GPTA, V2.0

The interconnections between the GPTA0/GPTA1/LTCA2 modules and the port I/O lines

are controlled in the port logics. The following port control operations selections must be

executed:

• Input/output function selection (IOCR registers)

• Pad driver characteristics selection for outputs (PDR registers)

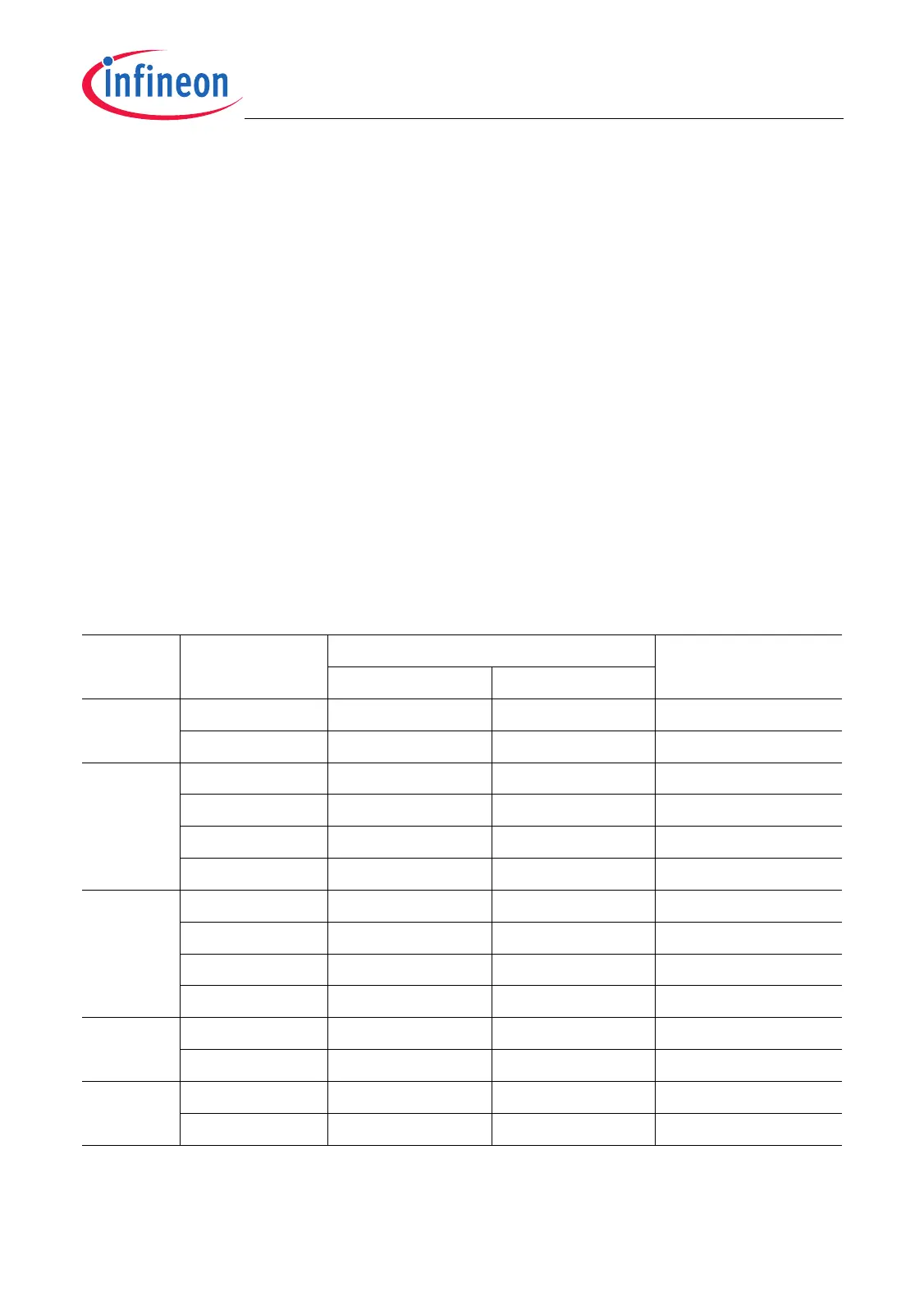

24.6.3.2 Input/Output Function Selection

The port input/output control registers contain bit fields that select the digital output and

input driver characteristics such as port direction (input/output), pull-up/down device or

open-drain selection for outputs, and alternate output selections. The I/O lines for the

GPTA0/GPTA1/LTCA2 modules are controlled by the port input/output control registers

for Port 2, Port 3, Port 4, Port 8, and Port 9. Each of the input/output control registers

controls four port lines using a 4-bit wide bit field PCx (definitions see Table 24-25).

Table 24-24 shows which of the input/output control register bit field is related to a

specific GPTA0/GPTA1/LTCA2 module I/O line. Note that input P2.9/IN1 has special

connections (see Page 24-263).

Table 24-24 IOCR Assignment for GPTA Port Lines

Port Port Lines for

GPTA

GPTA I/O Lines Controlled by

IOCR Register

Input Output

Port 2 P2.[11:8] IN[3:0]

1)

1) There is a special connection provided for GPTA input line IN1 (see Page 24-263).

OUT[3:0] P2_IOCR8

P2.[15:12] IN[7:4] OUT[7:4] P2_IOCR12

Port 3 P3.[3:0] IN[11:8] OUT[11:8] P3_IOCR0

P3.[7:4] IN[15:12] OUT[15:12] P3_IOCR4

P3.[11:8] IN[19:16] OUT[19:16] P3_IOCR8

P3.[15:12] IN[23:20] OUT[23:20] P3_IOCR12

Port 4 P4.[3:0] IN[27:24] OUT[27:24] P4_IOCR0

P4.[7:4] IN[31:28] OUT[31:28] P4_IOCR4

P4.[11:8] IN[35:32] OUT[35:32] P4_IOCR8

P4.[15:12] IN[39:36] OUT[39:36] P4_IOCR12

Port 8 P8.[3:0] IN[43:40] OUT[43:40] P8_IOCR0

P8.[7:4] IN[47:44] OUT[47:44] P8_IOCR4

Port 9 P9.[3:0] IN[51:48] OUT[51:48] P9_IOCR0

P9.[7:4] IN[55:52] OUT[55:52] P9_IOCR4

Loading...

Loading...