TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-24 V2.0, 2007-07

CPU, V2.0

2.5 Program Memory Interface (PMI)

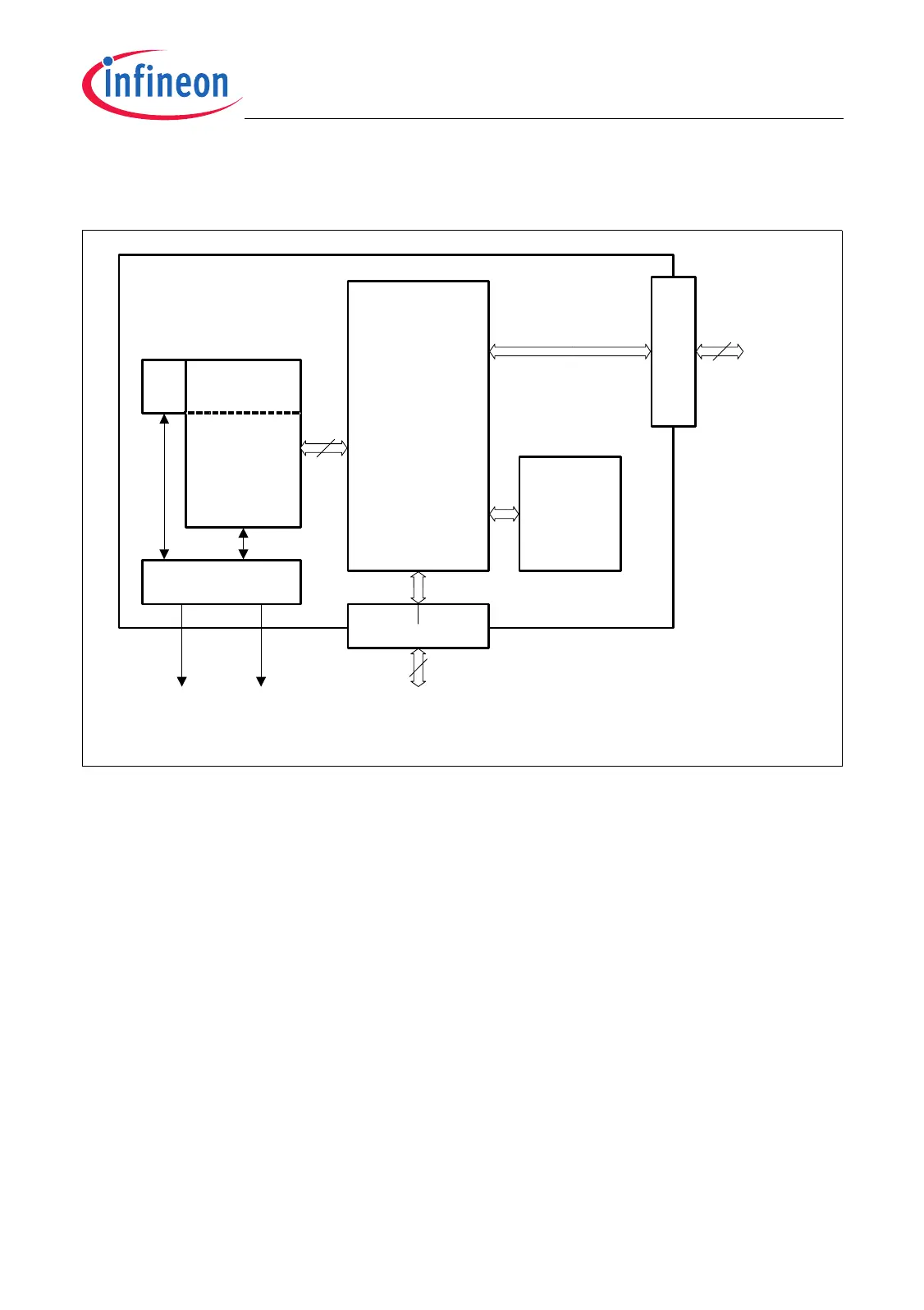

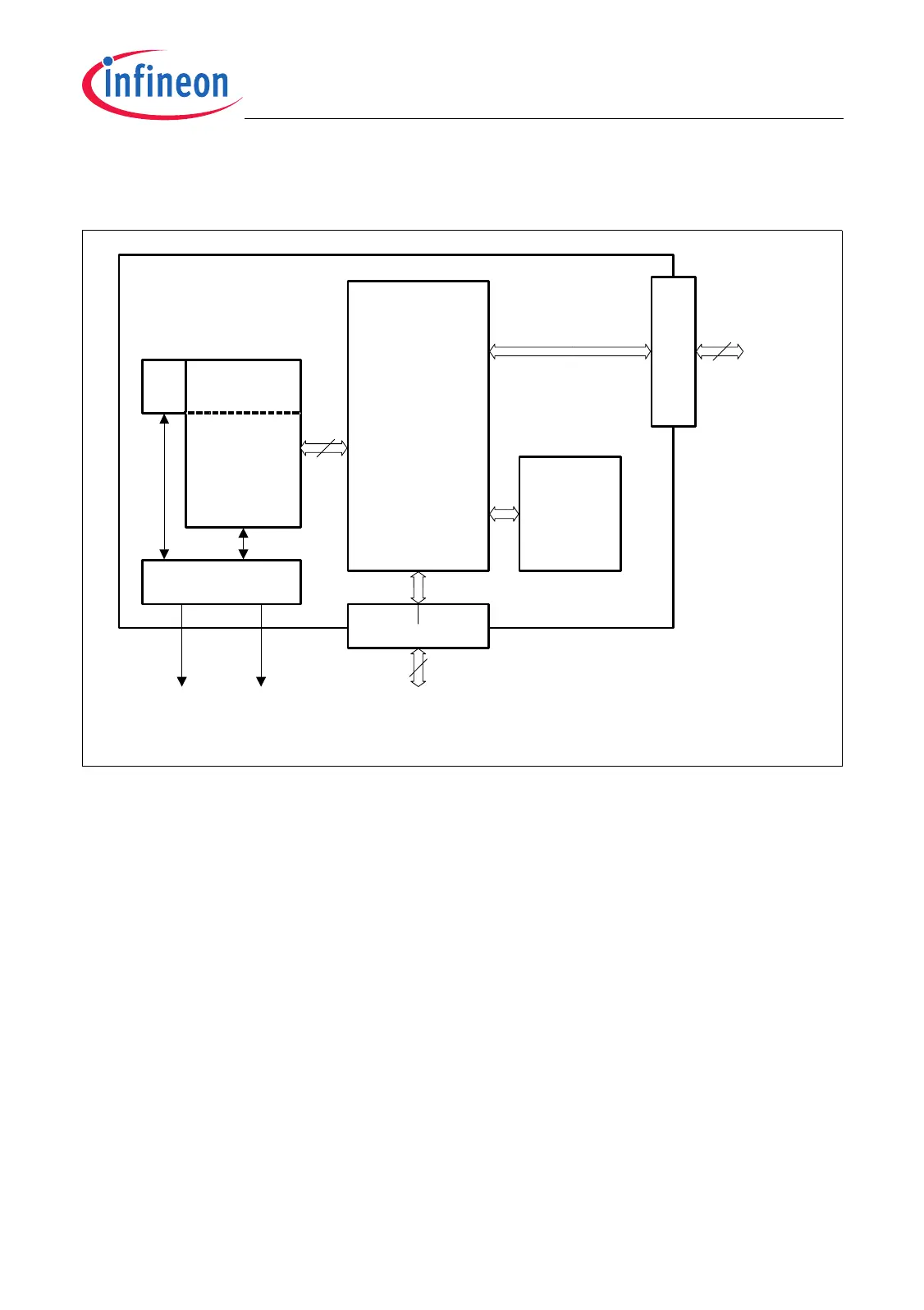

Figure 2-11 PMI Block Diagram

2.5.1 PMI Features

The Program Memory Interface (PMI) has the following features:

• 64 Kbyte memory as:

– 16 Kbyte instruction cache (ICACHE)

– 48 Kbyte scratch-pad RAM (SPRAM)

• ICACHE operation features:

– Two-way set associative cache

– LRU (Least-Recently Used) replacement algorithm

– Cache line size = 256 bits (4 double-words)

– Validity granularity (4 double-words per cache line)

– ICACHE can be globally invalidated to provide support for software cache

coherency (to be handled by the programmer).

– ICACHE can be bypassed to provide a direct fetch from the CPU to on-chip and

off-chip resources.

MCB05595

To/From Program

Local Memory Bus

128

Data Switch

&

Data Alignment

&

Interface Control

PMI

Control

Registers

64

PLMB Interface

Slave Master

128

CPU

Interface

64

To/From

CPU

Program Memory

Interface (PMI)

PMEM

Tag

RAM

16 KB

ICACHE

48 KB

SPRAM

To SCU

(PMI Memory Parity Errors)

Parity

Control/Check

PMEM = Program Memory in PMI

ICACHE = Instruction Cache

SPRAM = Scratch-Pad RAM

PLMB = Program Local Memory Bus

Loading...

Loading...