TC1796

Peripheral Units (Vol. 2 of 2)

Synchronous Serial Interface (SSC)

User’s Manual 20-16 V2.0, 2007-07

SSC, V2.1

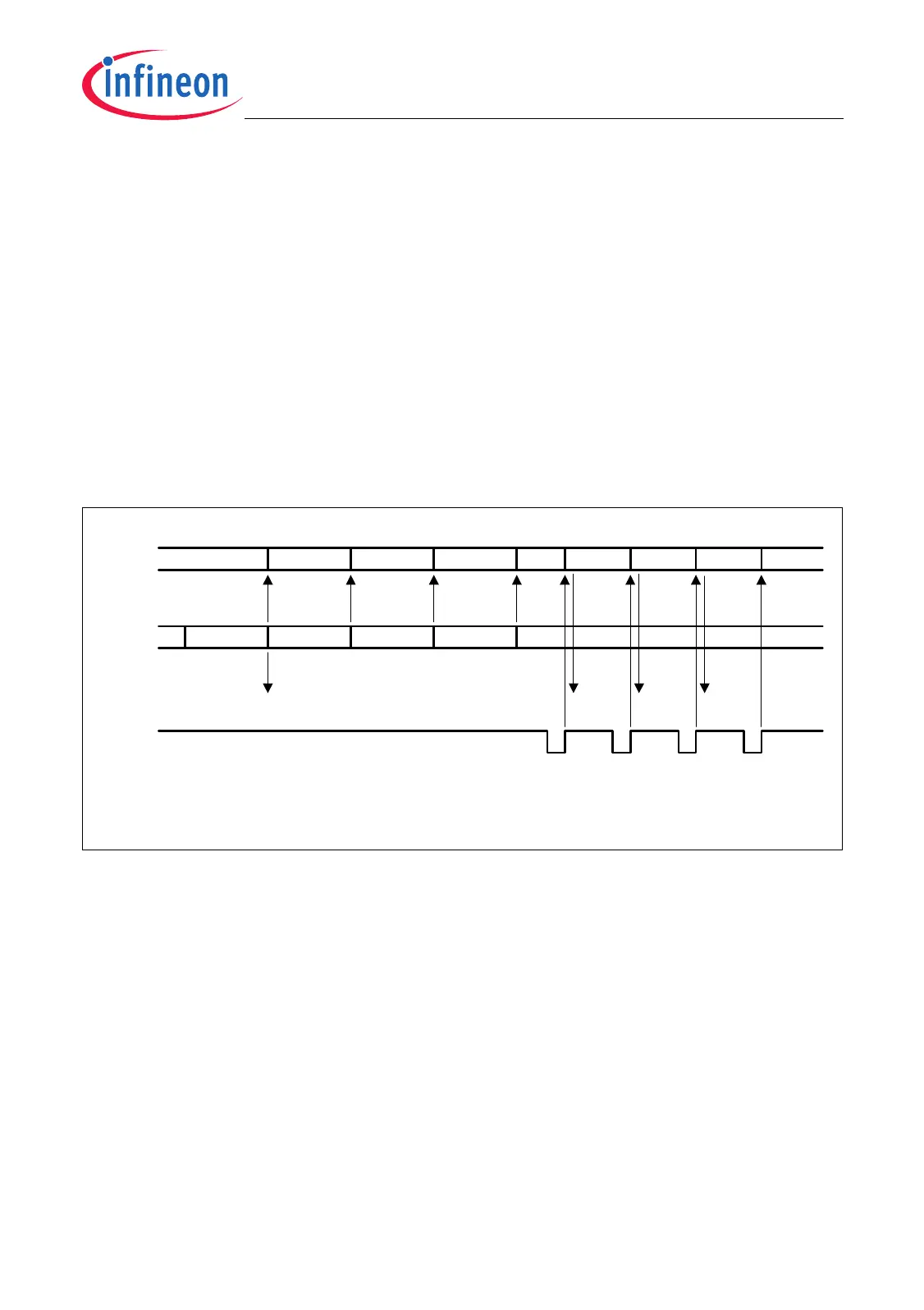

20.1.2.8 FIFO Transparent Mode

In Transparent Mode, a specific interrupt generation mechanism is used for receive and

transmit interrupts. In Transparent Mode, receive interrupts are always generated if data

bytes are available in the RXFIFO. The relevant conditions for interrupt generation in

Transparent Mode are:

• FIFO filling level

• Read/Write operations from/to the RB/TB data registers

Receive Operation

The interrupt generation for the RXFIFO depends on its filling level and the execution of

read operations of register RB (see Figure 20-8). Transparent Mode for the RXFIFO is

enabled when bits RXTMEN and RXFEN in register RXFCON are set.

Figure 20-8 Transparent Mode Receive FIFO Operation

If the RXFIFO is empty, a receive interrupt request RIR is always generated when the

first message is written into an empty RXFIFO (FSTAT.RXFFL changes from 0000

B

to

0001

B

). If the RXFIFO is filled with at least one message, the occurrence of further

receive interrupts depends on the read operations of register RB. The RIR will always be

activated after a RB read operation if the RXFIFO still contains data (FSTAT.RXFFL is

not equal to 0000

B

). If the RXFIFO is empty after a RB read operation, no further receive

interrupt will be generated.

If the RXFIFO is full (FSTAT.RXFFL = 1000

B

) and additional messages are received, a

receive interrupt request RIR will be generated. In this case, the message last written

into the RXFIFO is overwritten. If a RB read operation is executed with the RXFIFO

enabled but empty (underflow condition), an RIR will be generated as well, with bit

CON.RE set.

MCA05783

MRST

FSTAT.

RXFFL

011 000011010001000

Byte 1 Byte 2 Byte 3 Byte 4

RIR (1)

Read

RB

RIR (2)

100 010 001

RIR (3) RIR (4)

Read

Byte 1

Read

Byte 2

Read

Byte 3

Read

Byte 4

Loading...

Loading...