TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-51 V2.0, 2007-07

CPU, V2.0

2.7.2.4 Store Instruction Timing

Cache and Store instructions similar to Load instructions will have a result for the pre-

increment, post-increment, circular or bit-reverse addressing modes, but do not produce

a ‘memory’ result.

• Each instruction is single issued.

• The memory references is naturally aligned.

• The memory accessed takes a single cycle to accept a data item.

• Timing is best case; no cache misses, no pending stores.

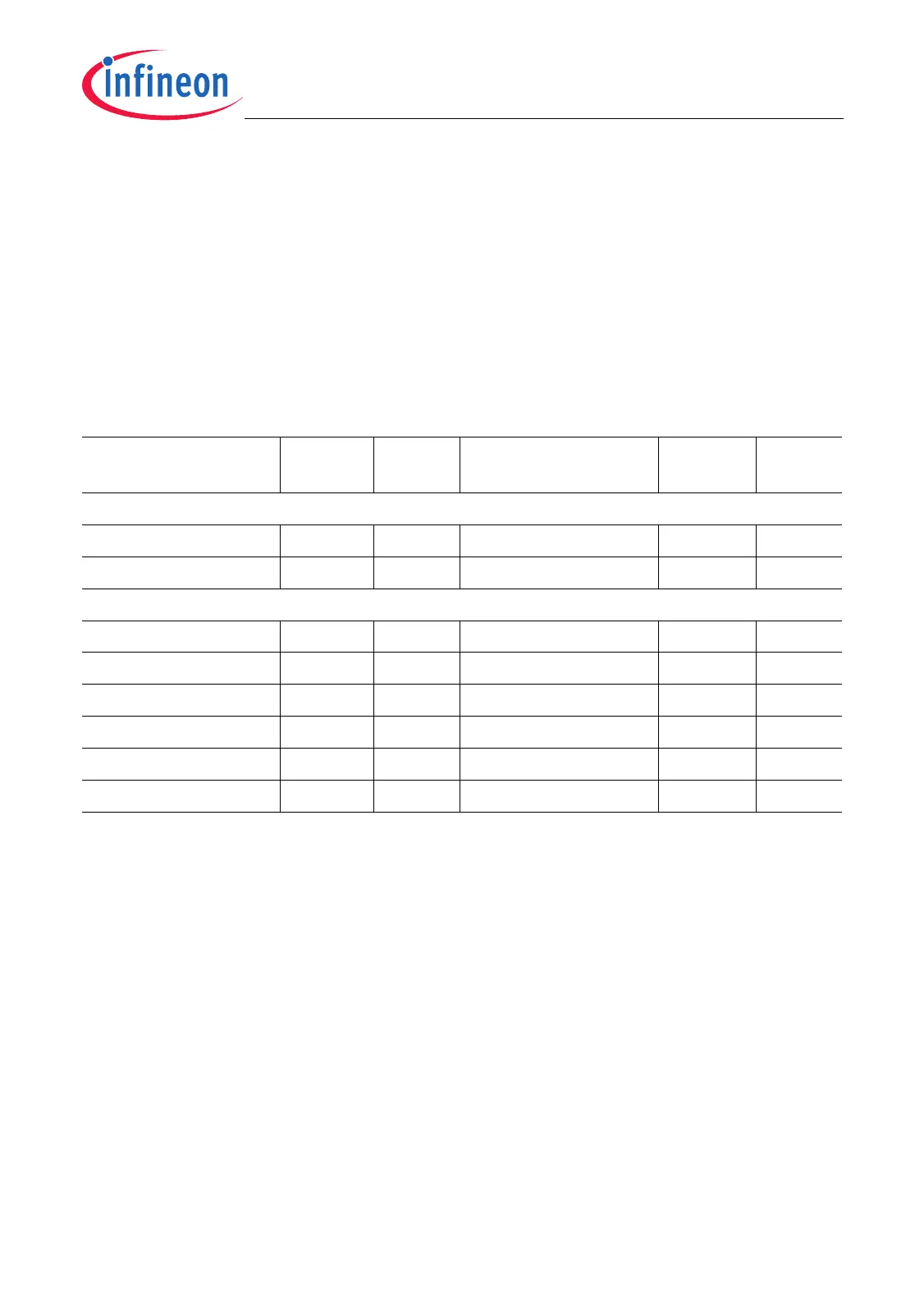

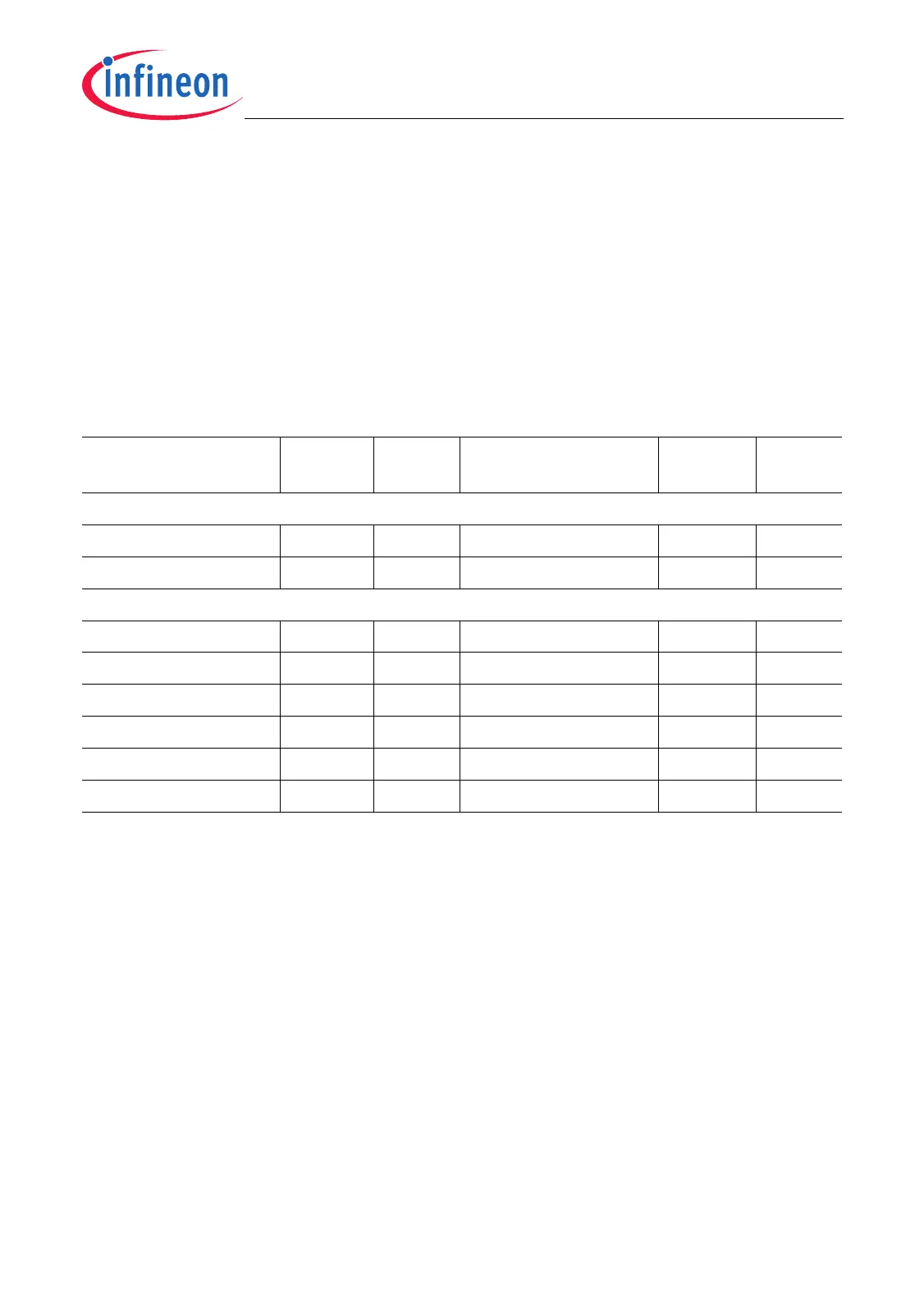

Table 2-17 Cache and Store Instruction Timing

Instruction Addr.

Latency

Repeat

Rate

Instruction Address

Latency

Repeat

Rate

Cache Instructions

CACHEA.I 11CACHEA.WI

1)

1) Repeat rate assumes that no memory writeback operation occurs. Otherwise the repeat rate will depend upon

the time for the castout buffers to clear.

11

CACHEA.W

1)

11

Store Instructions

ST.A 11ST.T 22

ST.B 11ST.W 11

ST.D 11STLCX 44

ST.DA 11STUCX 44

ST.H 11

ST.Q 11LDMST 22

Loading...

Loading...