TC1796

System Units (Vol. 1 of 2)

Peripheral Control Processor (PCP)

User’s Manual 11-59 V2.0, 2007-07

PCP, V2.0

11.10.4 PCP Error/Debug Status Register, PCP_ES

This is a read-only register, providing state information about error and debug conditions.

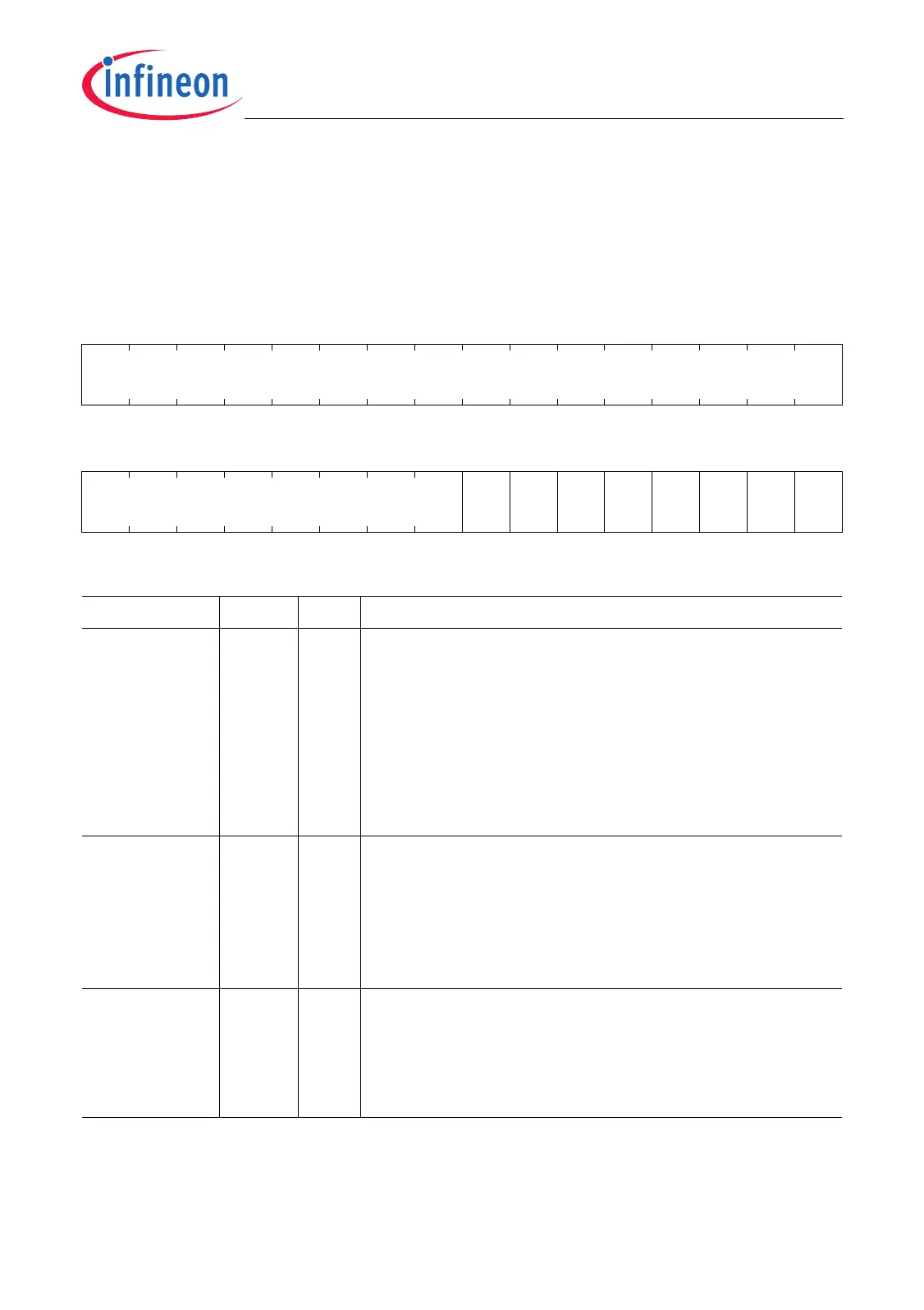

PCP_ES

PCP Error/Debug Status Register (14

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

EPC

rh

1514131211109876543210

EPN PPC CWD 0 DBE IAE DCR IOP BER

rh rh rh r rh rh rh rh rh

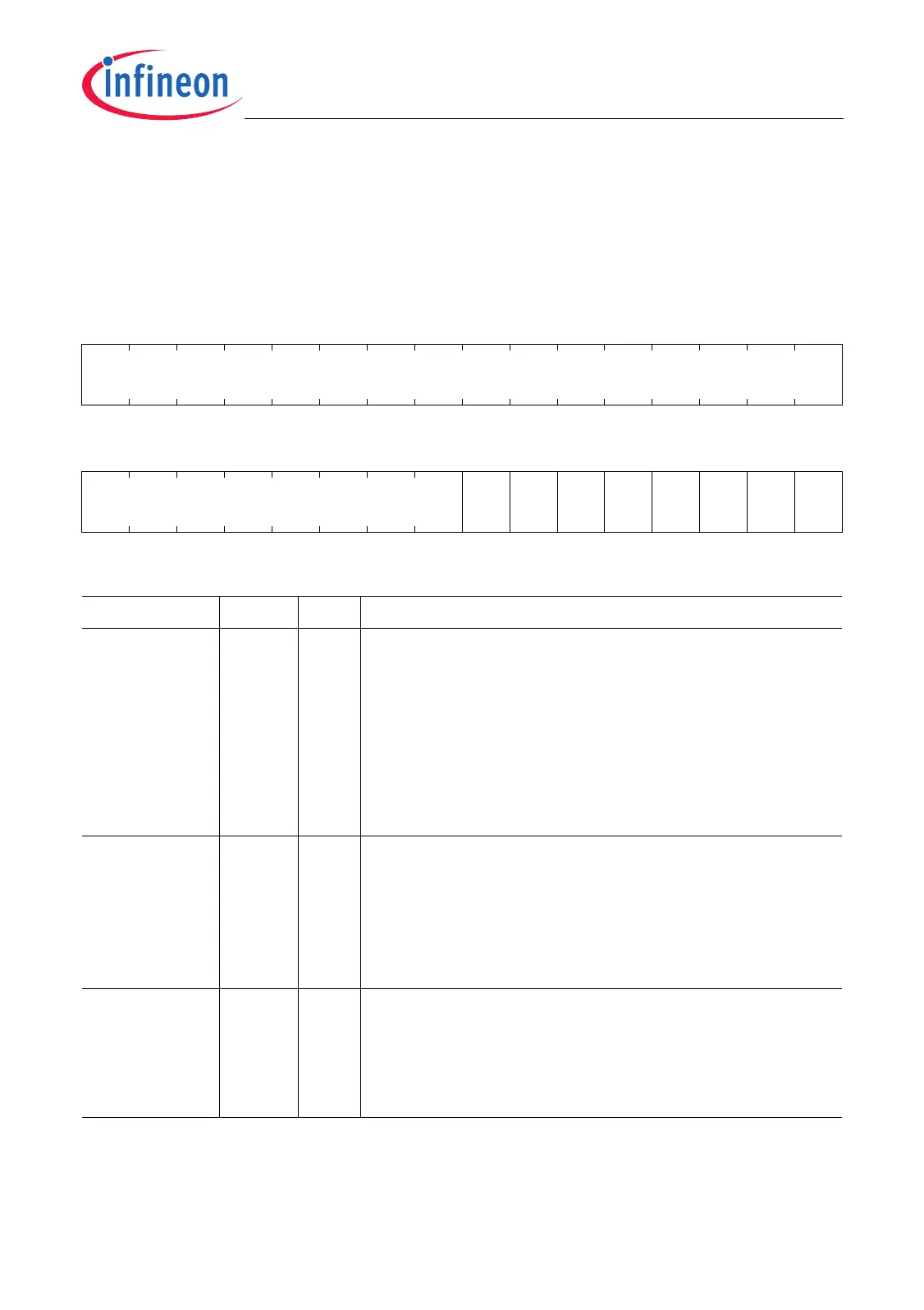

Field Bits Type Description

BER 0rhBus Error Flag

Set if the last error/debug event was an error

generated by an FPI Bus error or an invalid address

access; otherwise, clear.

Note: An FPI Bus error event does not cause the PCP

to post an error interrupt to the CPU. An FPI Bus

error interrupt is, however, generated by the FPI

control logic.

IOP 1rhInvalid Opcode

Set if the last error/debug event was an error

generated by the PCP attempting to execute an Invalid

Opcode (i.e. the value fetched from CMEM for

execution by the PCP did not represent a valid

instruction), otherwise clear.

DCR 2rhDisabled Channel Request Flag

Set if the last error/debug event was an error

generated by receipt of an interrupt request with an

SRPN that attempted to start a disabled PCP channel;

otherwise, clear.

Loading...

Loading...