TC1796

System Units (Vol. 1 of 2)

Direct Memory Access Controller

User’s Manual 12-39 V2.0, 2007-07

DMA, V2.0

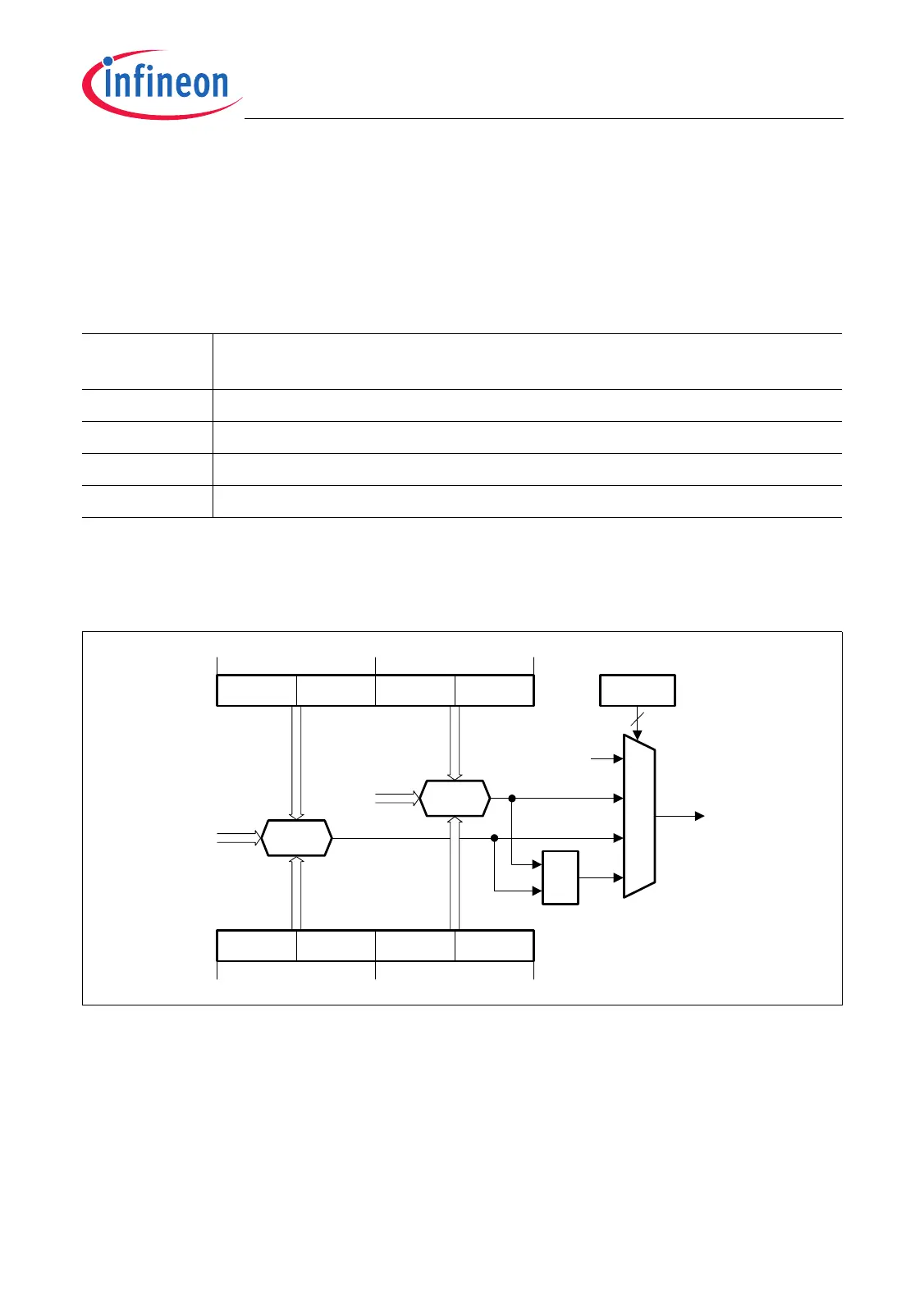

12.1.9.4 Pattern Detection for 32-bit Data Width

When 32-bit channel data width is selected (CHCRmn.CHDW = 10

B

), the pattern

detection logic is configured as shown in Figure 12-27. Three compare match

configurations are possible.

In 32-bit channel data width mode, the pattern detection logic makes it possible to

compare the lower half-word only, the upper half-word only, or the complete 32-bit word

with a pattern stored in the MEmPR register. A mask operation is not possible.

Figure 12-27 Pattern Detection for 32-bit Data Width (CHCRmn.CHDW = 10

B

)

Table 12-4 Pattern Detection for 32-bit Data Width

CHCRmn.

PATSEL

Pattern Detection Operating Modes

00

B

Pattern detection disabled

01

B

Unmasked pattern compare RDm[1:0] to PATm[1:0]

10

B

Unmasked pattern compare RDm[3:2] to PATm[3:2]

11

B

Unmasked pattern compare RDm[3:0] to PATm[3:0]

1516

MCA05704

0

PATm3 PATm2

PATm1 PATm0

31

RDm3 RDm2 RDm1 RDm0

31

0

COMP

COMP

2

&

PATSEL

CHCRmn

Pattern

Detected

0

MEmR

MEmPR

1516

0

Mask

0

Mask

00

01

10

11

Loading...

Loading...