TC1796

System Units (Vol. 1 of 2)

Direct Memory Access Controller

User’s Manual 12-76 V2.0, 2007-07

DMA, V2.0

12.2.4 Channel Control/Status Registers

The Channel Control Register for DMA channel mx contains its configuration and its

control bits and bit fields.

DMA_CHCR0x (x = 0-7)

DMA Channel 0x Control Register

(x*20

H

+84

H

) Reset Value: 0000 0000

H

DMA_CHCR1x (x = 0-7)

DMA Channel 1x Control Register

(x*20

H

+184

H

) Reset Value: 0000 0000

H

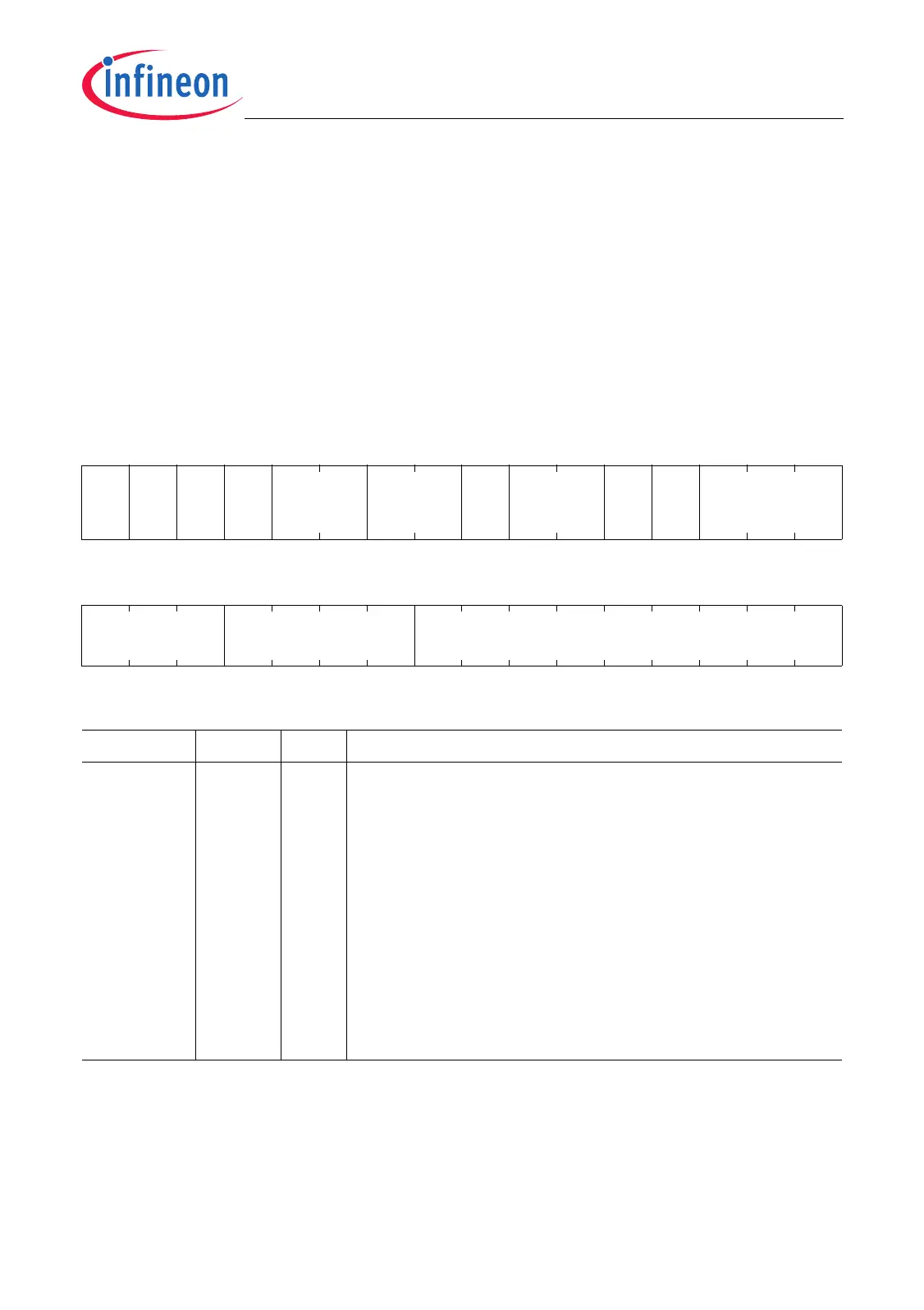

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

DMA

PRIO

0

CH

PRIO

0 PATSEL 0 CHDW

CH

MO

DE

RRO

AT

BLKM

r rw r rw r rw r rw rw rw rw

1514131211109876543210

PRSEL 0 TREL

rw r rw

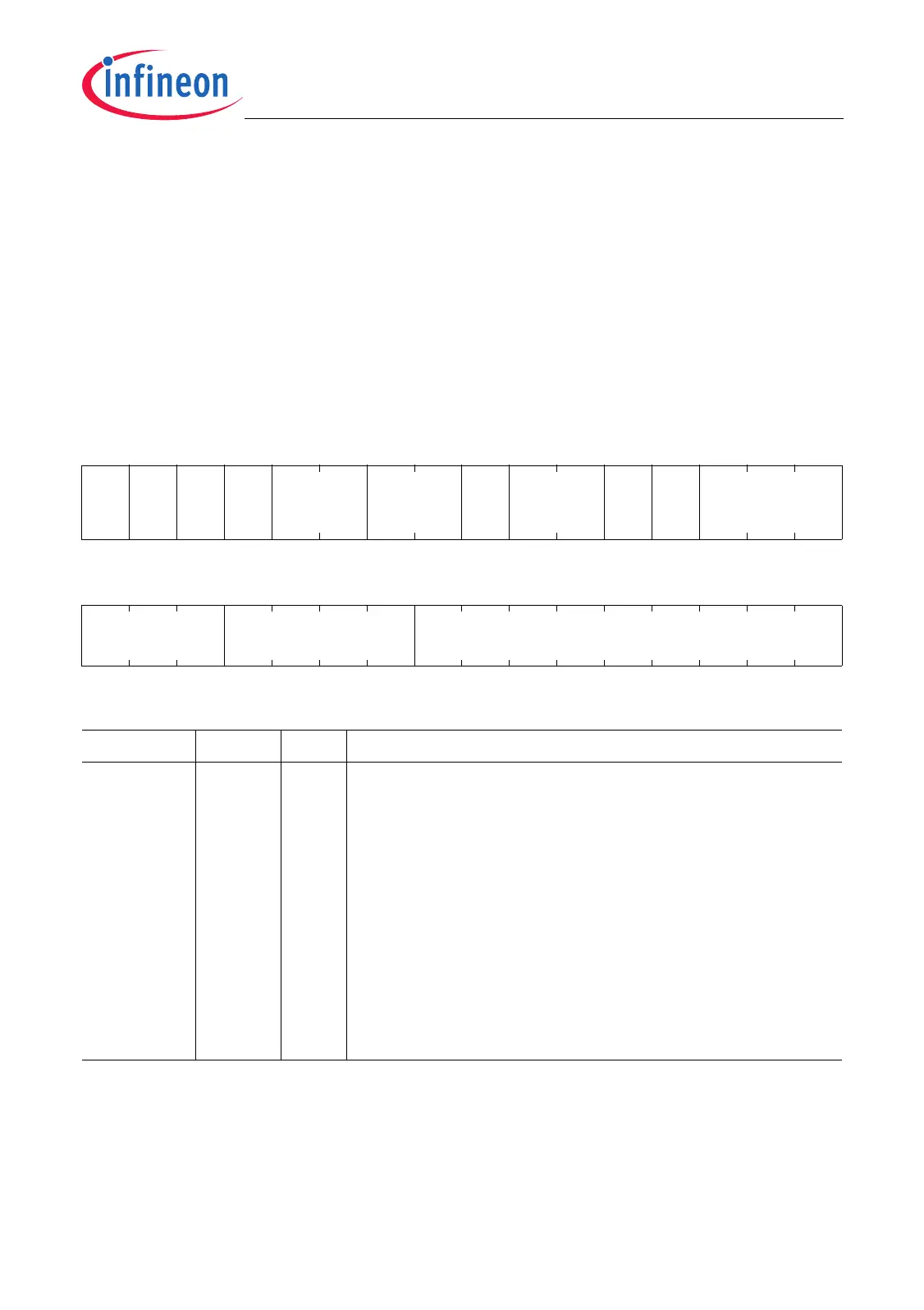

Field Bits Type Description

TREL [8:0] rw Transfer Reload Value

This bit field contains the number of DMA transfers for s

DMA transaction of DMA channel mx. This 9-bit transfer

count value is loaded into CHSRmx.TCOUNT at the

start of a DMA transaction (when TRSR.CHmx

becomes set and CHSRmx.TCOUNT = 0). TREL can

be written during a running DMA transaction because

TCOUNT will be updated (decremented) during the

DMA transaction.

If TREL = 0 or if TREL = 1, TCOUNT will be loaded with

1 when a new transaction is started (at least one DMA

transfer must be executed per DMA transaction).

Loading...

Loading...