TC1796

Peripheral Units (Vol. 2 of 2)

Micro Link Interface (MLI)

User’s Manual 23-105 V2.0, 2007-07

MLI, V2.0

23.4.6 Transmitter Interrupt Registers

The Transmitter Interrupt Enable Register TIER contains the interrupt enable bits and

the clear bits for all transmitter events. The bits marked w always read as 0.

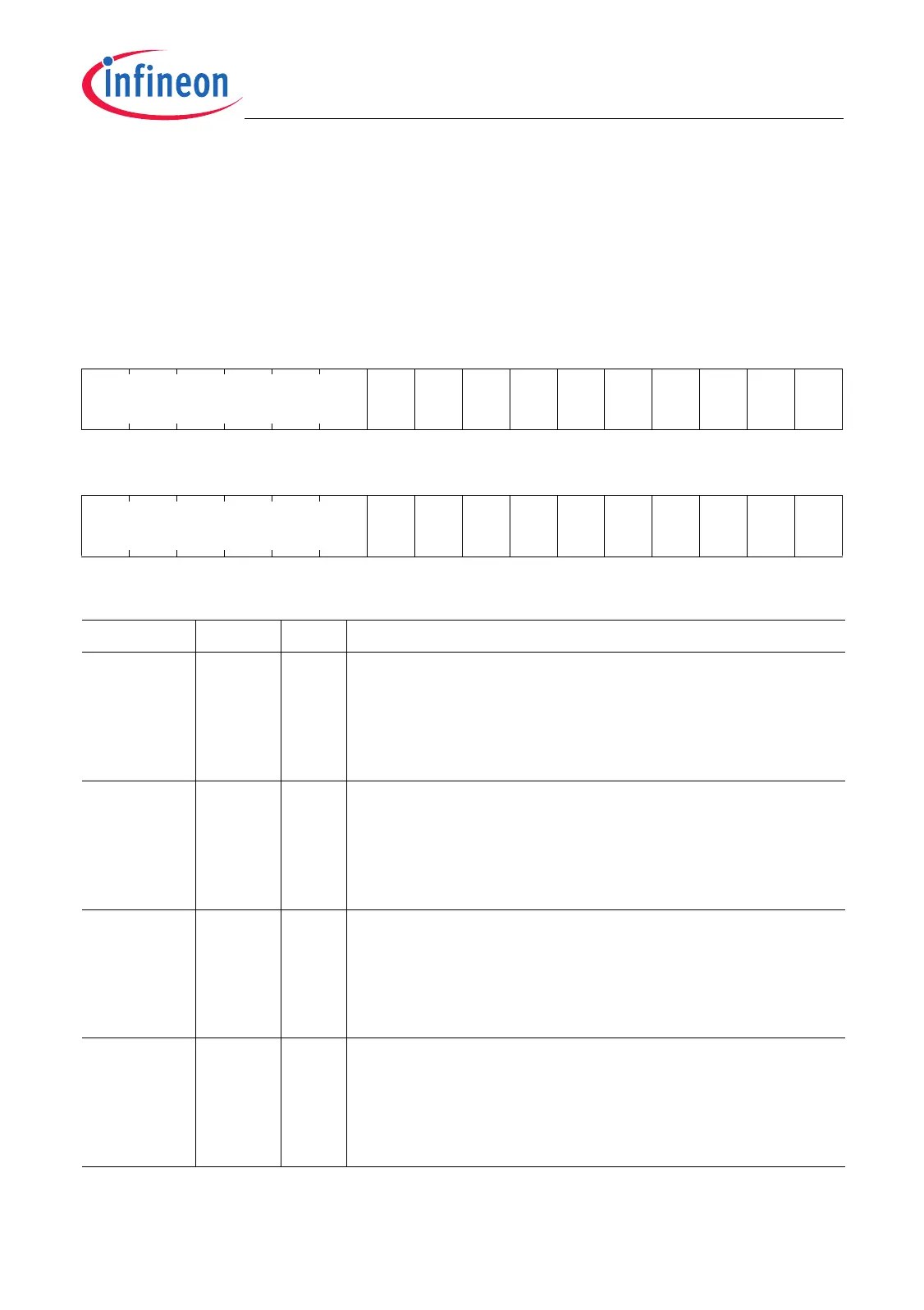

TIER

Transmitter Interrupt Enable Register (98

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

TE

IR

PE

IR

CFS

IR3

CFS

IR2

CFS

IR1

CFS

IR0

NFS

IR3

NFS

IR2

NFS

IR1

NFS

IR0

r wwwwwwwwww

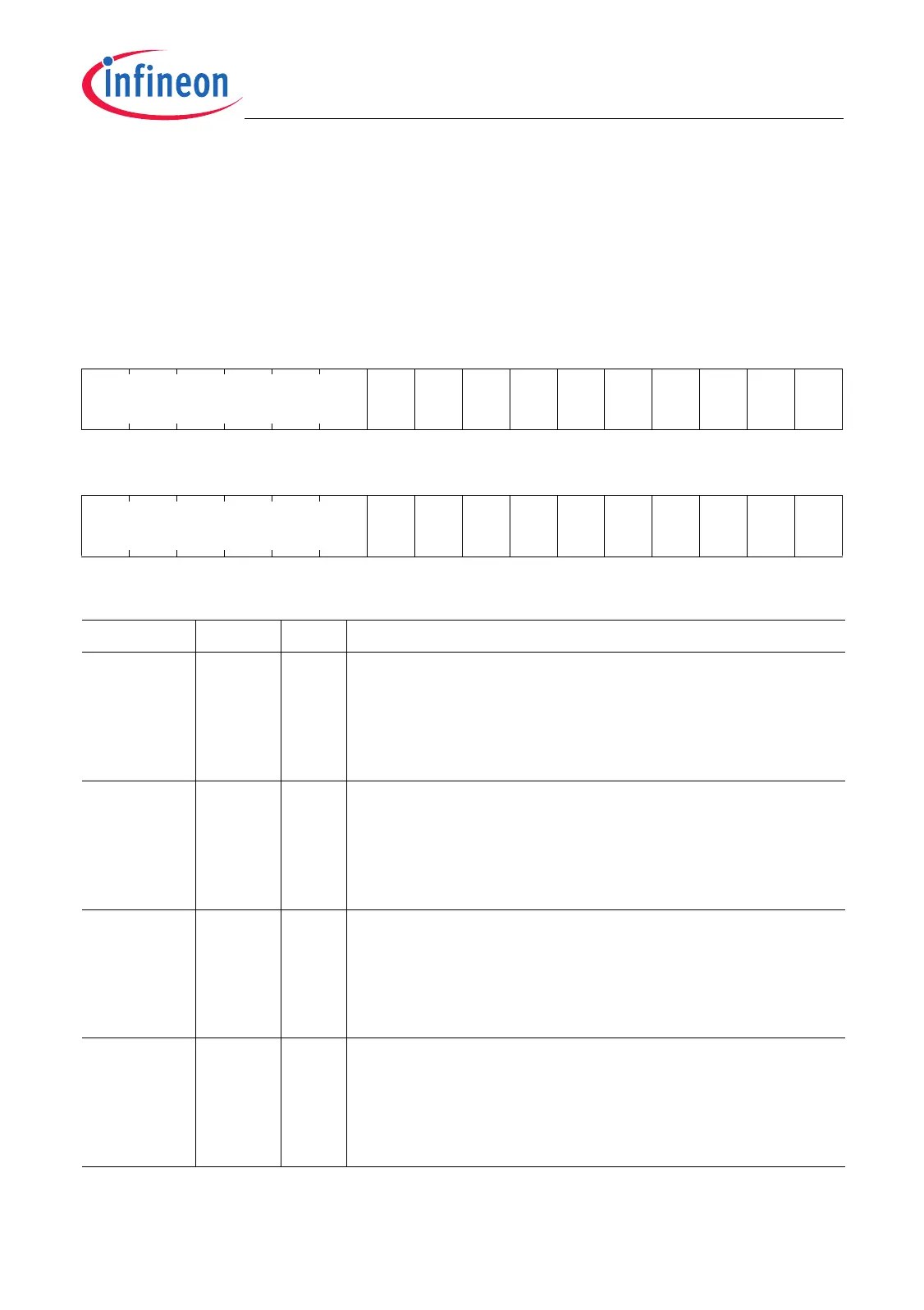

1514131211109876543210

0

TE

IE

PE

IE

CFS

IE3

CFS

IE2

CFS

IE1

CFS

IE0

NFS

IE3

NFS

IE2

NFS

IE1

NFS

IE0

r rwrwrwrwrwrwrwrwrwrw

Field Bits Type Description

NFSIEx

(x = 0-3)

xrwNormal Frame Sent in Pipe x Interrupt Enable

0

B

Normal frame sent in pipe x event is disabled for

activation of an SRx line.

1

B

Normal frame sent in pipe x event is enabled for

activation of an SRx line.

CFSIEx

(x = 0-3)

4 + x rw Command Frame Sent in Pipe x Interrupt Enable

0

B

Command frame sent in pipe x event is disabled

for activation of an SRx line.

1

B

Command frame sent in pipe x event is enabled

for activation of an SRx line.

PEIE 8rwParity Error Interrupt Enable

0

B

Parity error event is disabled for activation of an

SRx line.

1

B

Parity error event is enabled for activation of an

SRx line.

TEIE 9rwTime-Out Error Interrupt Enable

0

B

Time-out error event is disabled for activation of

an SRx line.

1

B

Time-out error event is enabled for activation of an

SRx line.

Loading...

Loading...