TC1796

System Units (Vol. 1 of 2)

LMB External Bus Unit

User’s Manual 13-86 V2.0, 2007-07

EBU, V2.0

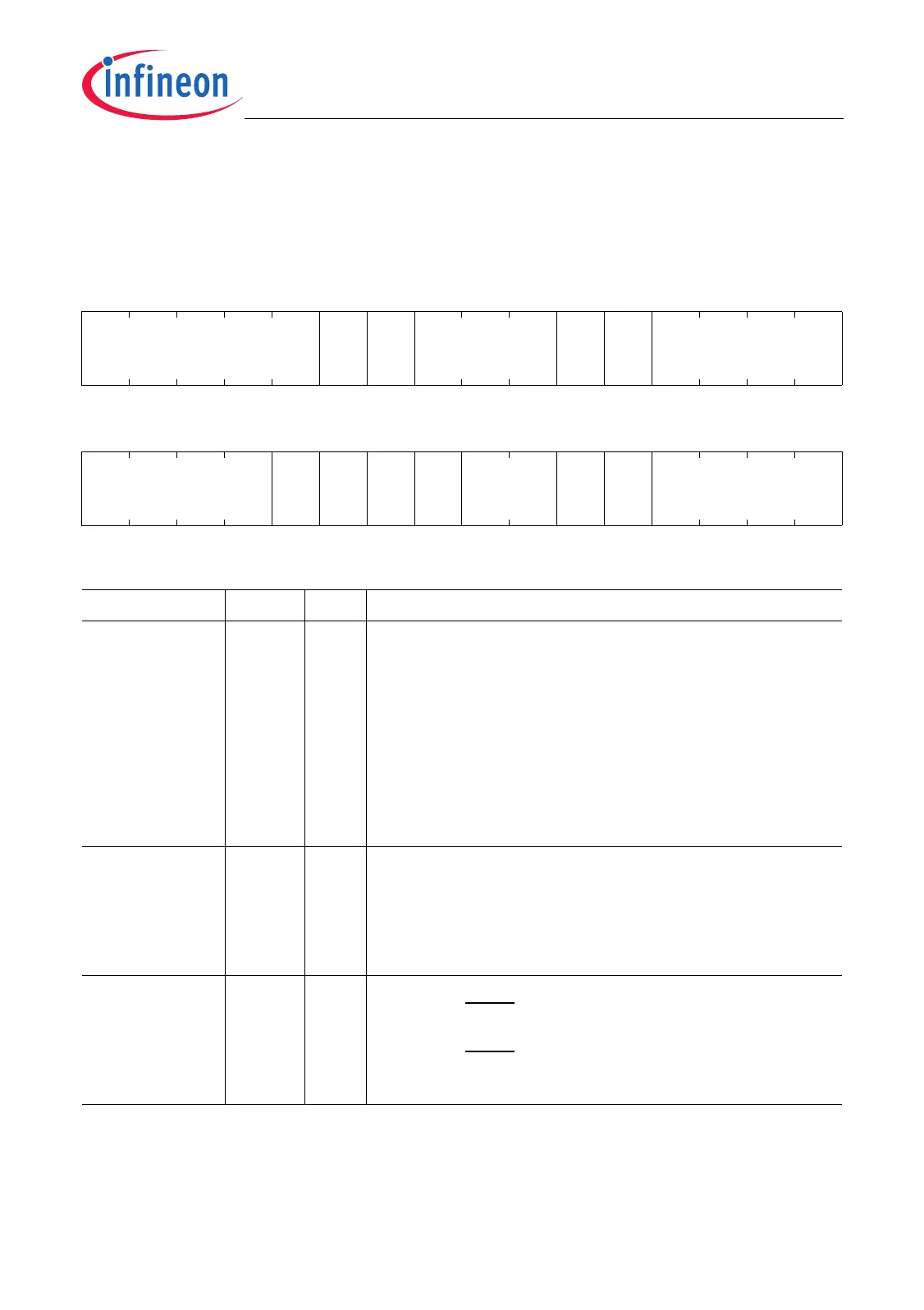

13.10.4 Burst Flash Control Register, BFCON

EBU_BFCON

EBU Burst Flash Control Register (020

H

) Reset Value: 0010 01D0

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

DBA

1

EBS

E1

0

WAI

TFU

NC1

FBB

MSE

L1

FETBLEN1

r rw rw r rw rw rw

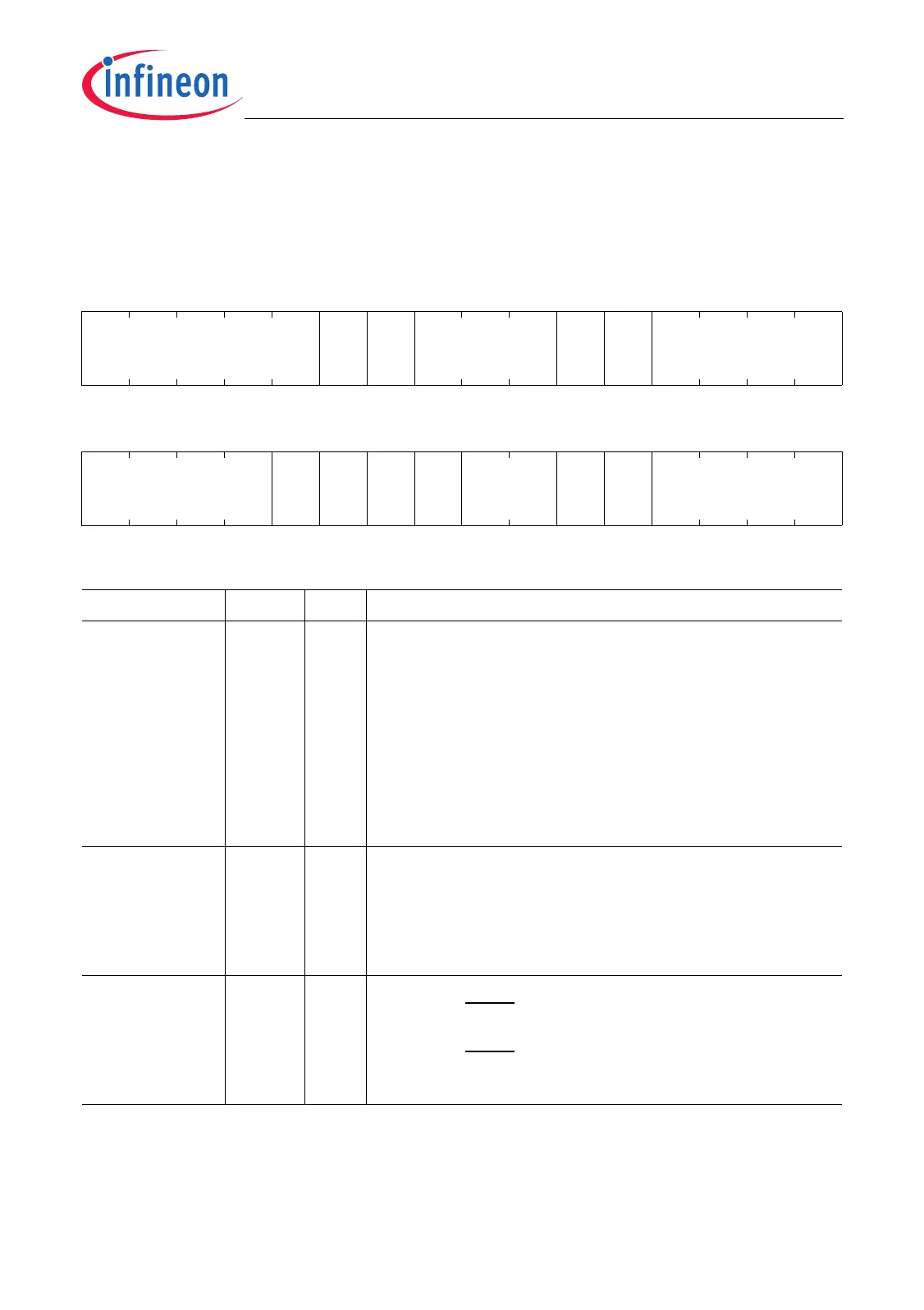

1514131211109876543210

DTALTNCY

FDB

KEN

DBA

0

EBS

E0

BFC

MSE

L

EXT

CLOCK

WAI

TFU

NC0

FBB

MSE

L0

FETBLEN0

rw rw rw rw rw rw rw rw rw

Field Bits Type Description

FETBLEN0 [3:0] rw Fetch Burst Length for Burst Flash Type 0

This bit field determines the maximum number of

burst data cycles which are executed by the EBU

during a burst access to Burst Flash Type 0.

000

B

1 data access (default after reset).

001

B

2 data accesses.

010

B

4 data accesses.

011

B

8 data accesses.

1XX

B

Reserved.

FBBMSEL0 4rwFlash Burst Buffer Mode Select for Burst Flash

Type 0

0

B

Continuous mode selected

1

B

Flash burst buffer length defined by value in

FETBLEN0 (default after reset)

WAITFUNC0 5rwFunction of WAIT input for Burst Flash Type 0

0

B

The WAIT input operates as a wait data bus

function on bursts (default after reset).

1

B

The WAIT input operates as a terminate burst

function.

Loading...

Loading...