TC1796

System Units (Vol. 1 of 2)

Clock System and Control

User’s Manual 3-35 V2.0, 2007-07

Clock, V2.0

3.3.3.3 Fractional Divider Register

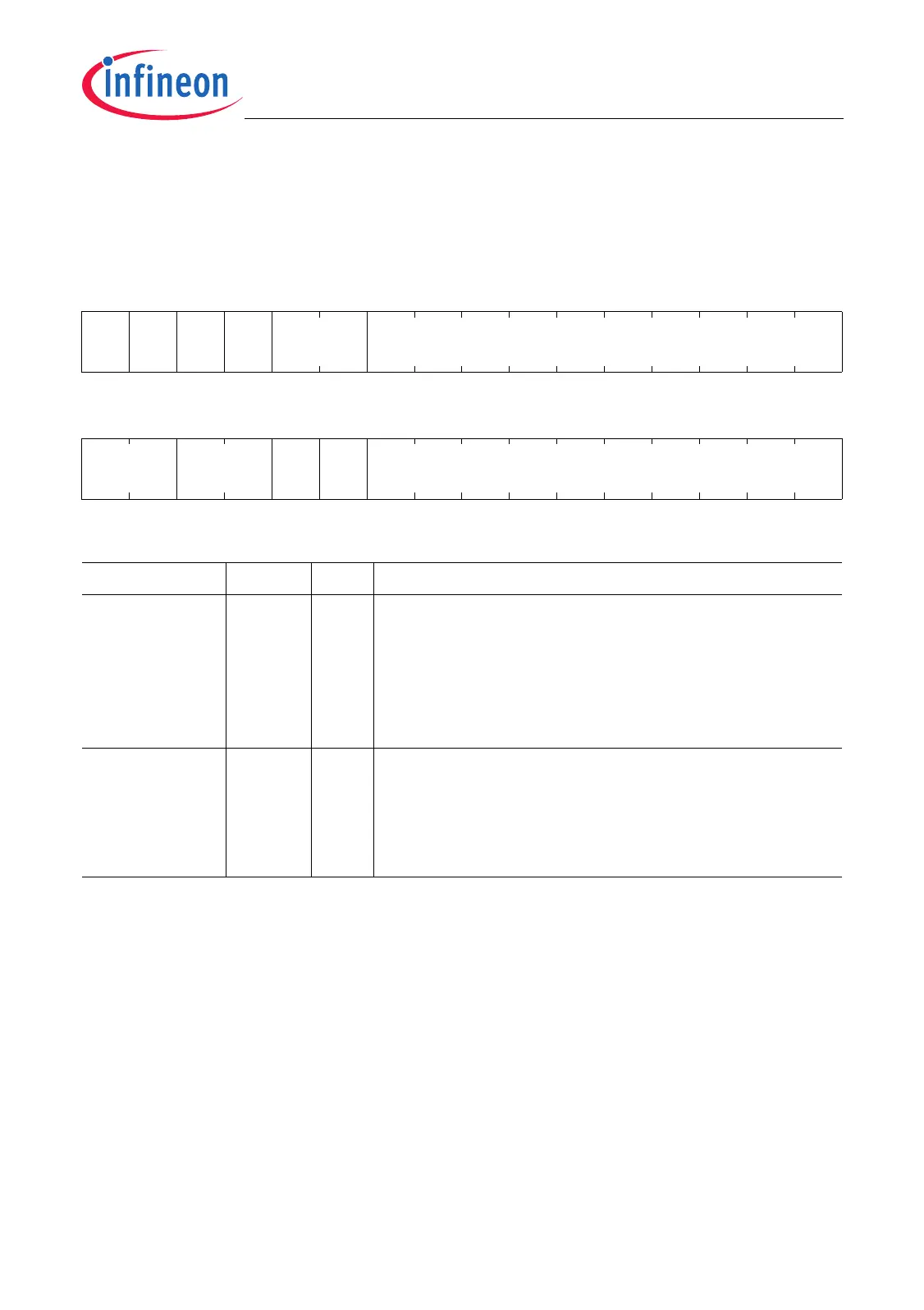

FDR

Fractional Divider Register Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DIS

CLK

EN

HW

SUS

REQ

SUS

ACK

0 RESULT

rwh rw rh rh r rh

1514131211109876543210

DM SC SM 0 STEP

rw rw rw r rw

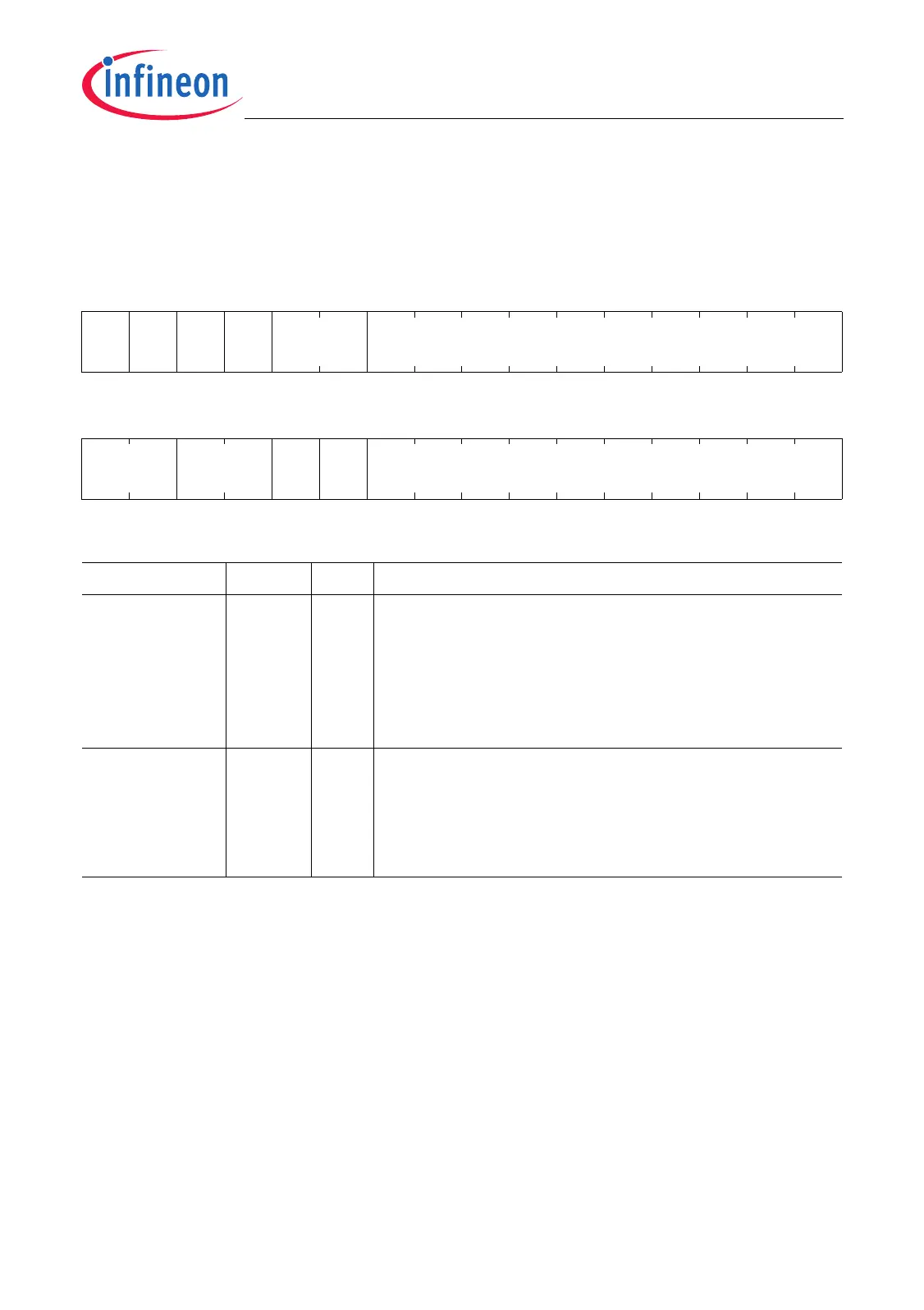

Field Bits Type Description

STEP [9:0] rw Step Value

In normal divider mode, STEP contains the reload

value for RESULT.

In fractional divider mode, this bit field determines

the 10-bit value that is added to RESULT with each

input clock cycle.

SM 11 rw Suspend Mode

SM selects between granted or immediate suspend

mode.

0

B

Granted suspend mode selected

1

B

Immediate suspend mode selected

Loading...

Loading...