TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-155 V2.0, 2007-07

GPTA, V2.0

24.3.2 FPC Registers

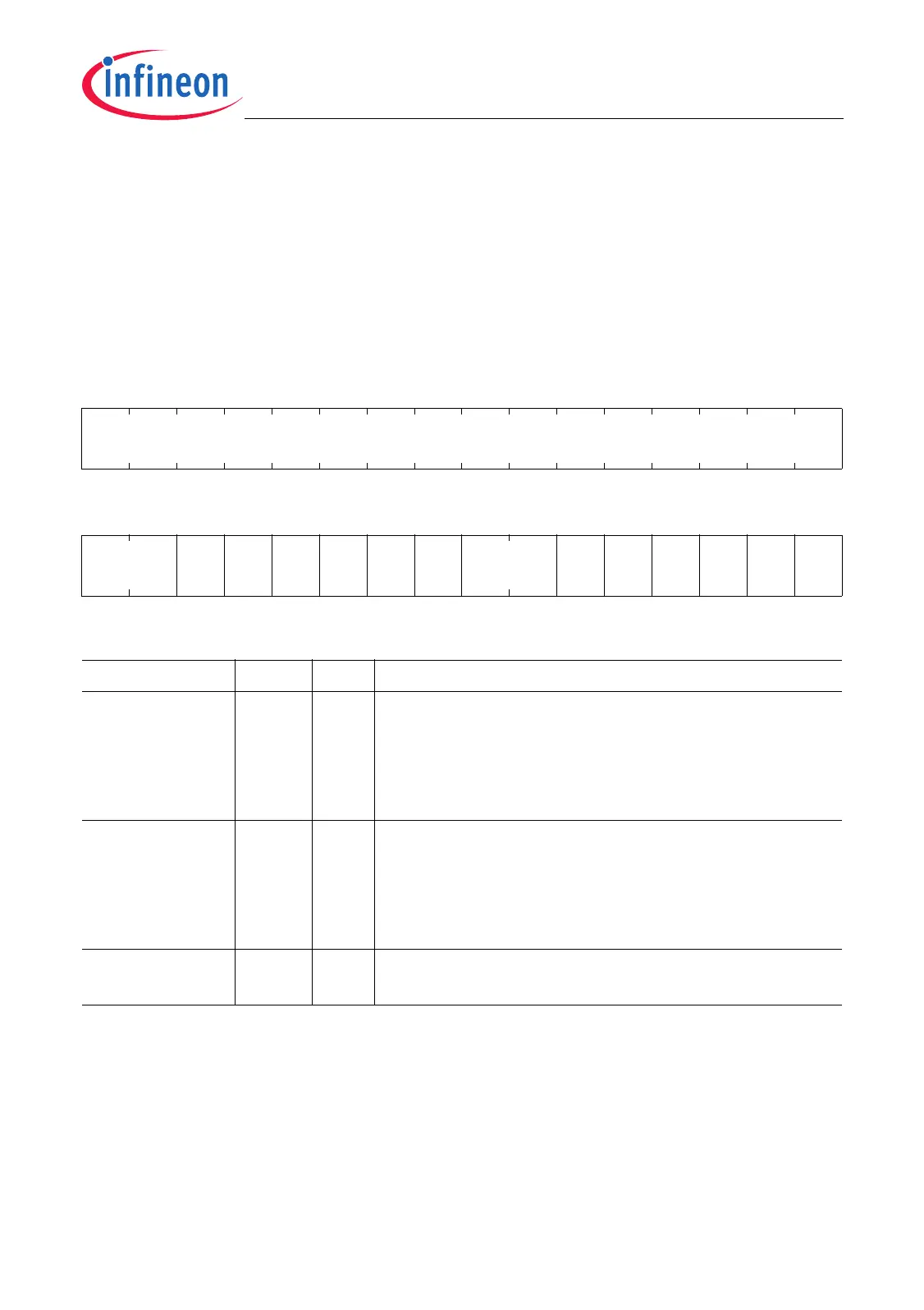

GPTA0_FPCSTAT

GPTA0 Filter and Prescaler Cell Status Register

(044

H

) Reset Value: 0000 0000

H

GPTA1_FPCSTAT

GPTA1 Filter and Prescaler Cell Status Register

(044

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0

FEG

5

FEG

4

FEG

3

FEG

2

FEG

1

FEG

0

0

REG

5

REG

4

REG

3

REG

2

REG

1

REG

0

r rwh rwh rwh rwh rwh rwh r rwh rwh rwh rwh rwh rwh

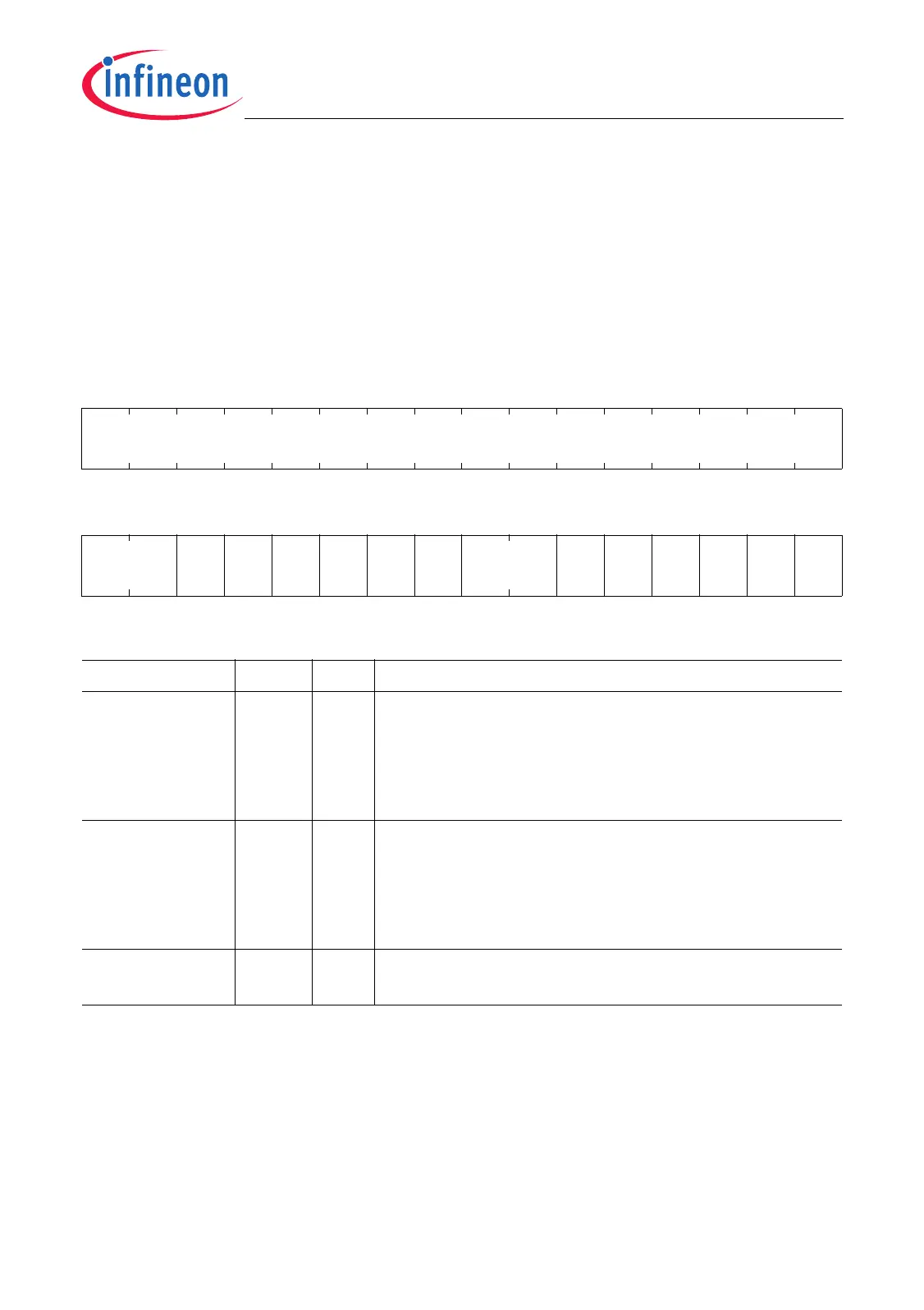

Field Bits Type Description

REGk

(k = 0-5)

krwhRising Edge Glitch Flag for FPCk

0

B

No rising edge of glitch detected during

filtering

1

B

Rising edge of glitch detected during filtering

Bits REGk are bit protected (see Section 24.3.2).

FEGk

(k = 0-5)

k+8 rwh Falling Edge Glitch Flag for FPCk

0

B

No falling edge of glitch detected during

filtering

1

B

Falling edge of glitch detected during filtering

Bits FEGk are bit protected (see Section 24.3.2).

0 [7:6],

[31:14]

r Reserved

Read as 0; should be written with 0.

Loading...

Loading...