TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual 22-20 V2.0, 2007-07

MultiCAN, V2.0

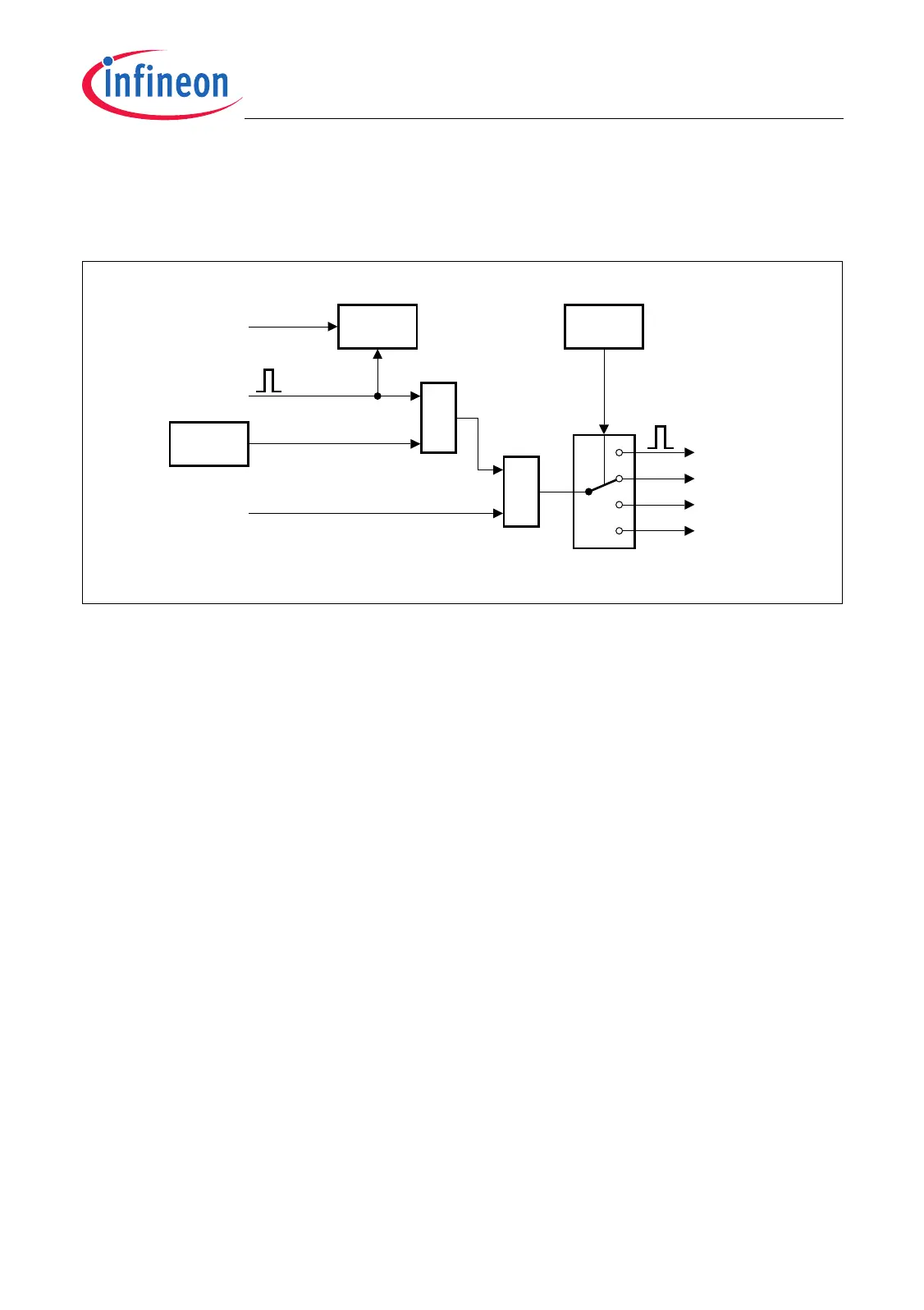

module. If more than one interrupt source is connected to the same interrupt node

pointer (in the interrupt node pointer register), the requests are combined to one

common line.

Figure 22-8 General Interrupt Structure

22.3.2 Clock Control

The CAN module timer clock f

CAN

of the functional blocks of the MultiCAN module is

derived from the module control clock f

CLC

. The Fractional Divider is used to generate

f

CAN

used for the bit timing calculation, the generation of the NTU, and the local time of

the TTCAN part. The frequency of f

CAN

is identical for all CAN nodes. The TTCAN

scheduler and the register file operate with the module control clock f

CLC

. See also

“Module Clock Generation” on Page 22-201.

The output clock f

CAN

of the Fractional Divider is based on the system clock f

CLC

, but only

every n-th clock pulse is taken. A suspend signal (coming as acknowledge from the

MultiCAN module in response to a OCDS suspend request) freezes or resets the

Fractional Divider.

MCA05834_mod

Interrupt

Flag

Writing 0

Interrupt

Enable

&Interrupt Event

Set

Clear

Other Interrupt

Sources on the

same INP

INP

To INT_O0

To INT_O1

.....

To INT_O15

≥1

Loading...

Loading...