TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-273 V2.0, 2007-07

GPTA, V2.0

24.6.7 Interrupt Registers

Each of the service request outputs of the GPTA0, GPTA1 and LTCA2 module kernels

is able to generate an interrupt and is controlled by an interrupt service request control

register GPTA_SRCk. Therefore, the following interrupt service request control registers

are available:

• GPTA0: GPTA0_SRC[37:00]

• GPTA1: GPTA1_SRC[37:00]

• LTCA2: LTCA2_SRC[15:00]

GPTA0_SRCk (k = 00-37)

GPTA0 Interrupt Service Request Control Register k

(7FC

H

-k*4

H

) Reset Value: 0000 0000

H

GPTA1_SRCk (k = 00-37)

GPTA1 Interrupt Service Request Control Register k

(7FC

H

-k*4

H

) Reset Value: 0000 0000

H

LTCA2_SRCk (k = 00-15)

LTCA2 Interrupt Service Request Control Register k

(7FC

H

-k*4

H

) Reset Value: 0000 0000

H

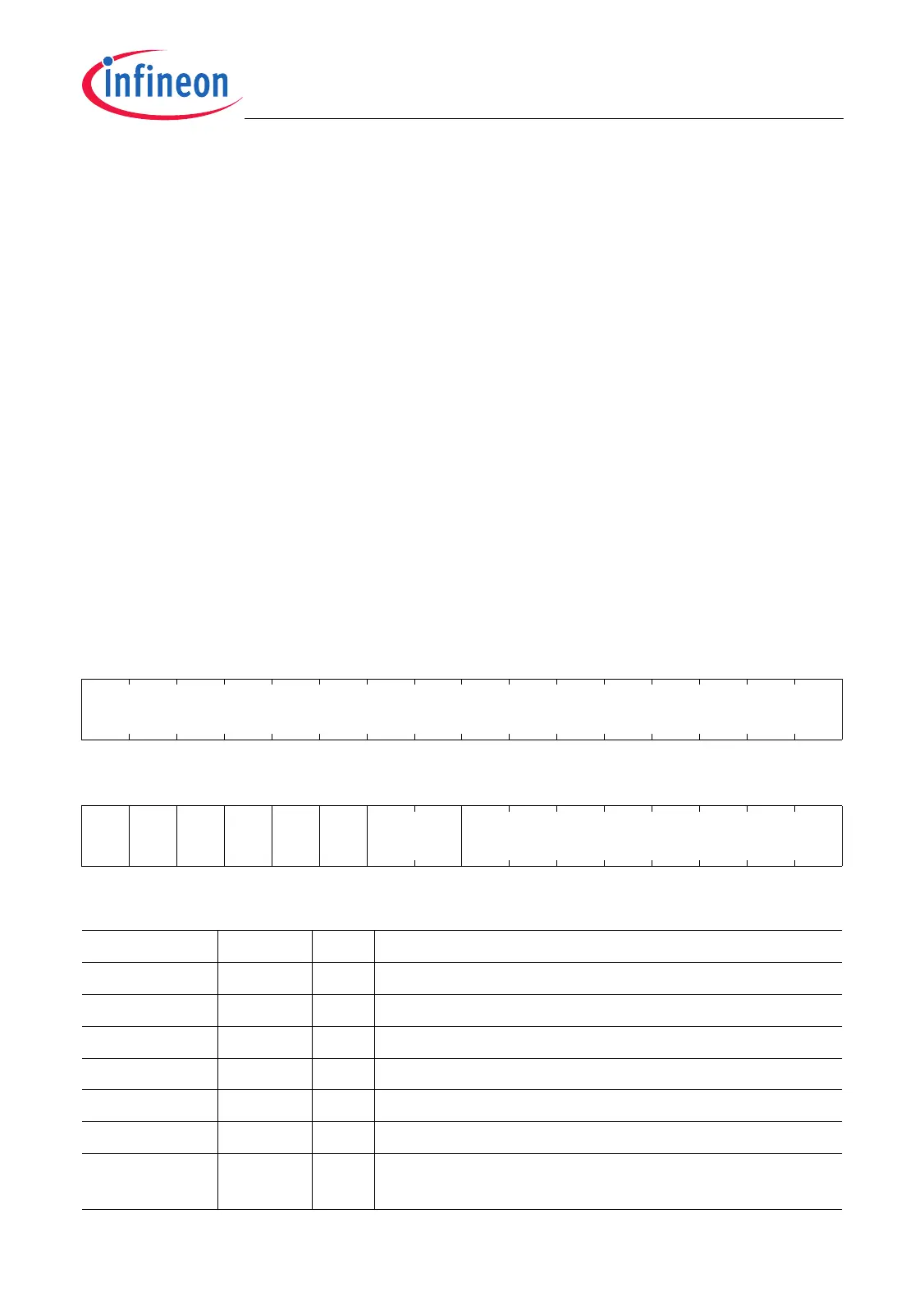

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

SET

R

CLR

R

SRR SRE 0 TOS 0 SRPN

w w rh rw r rw r rw

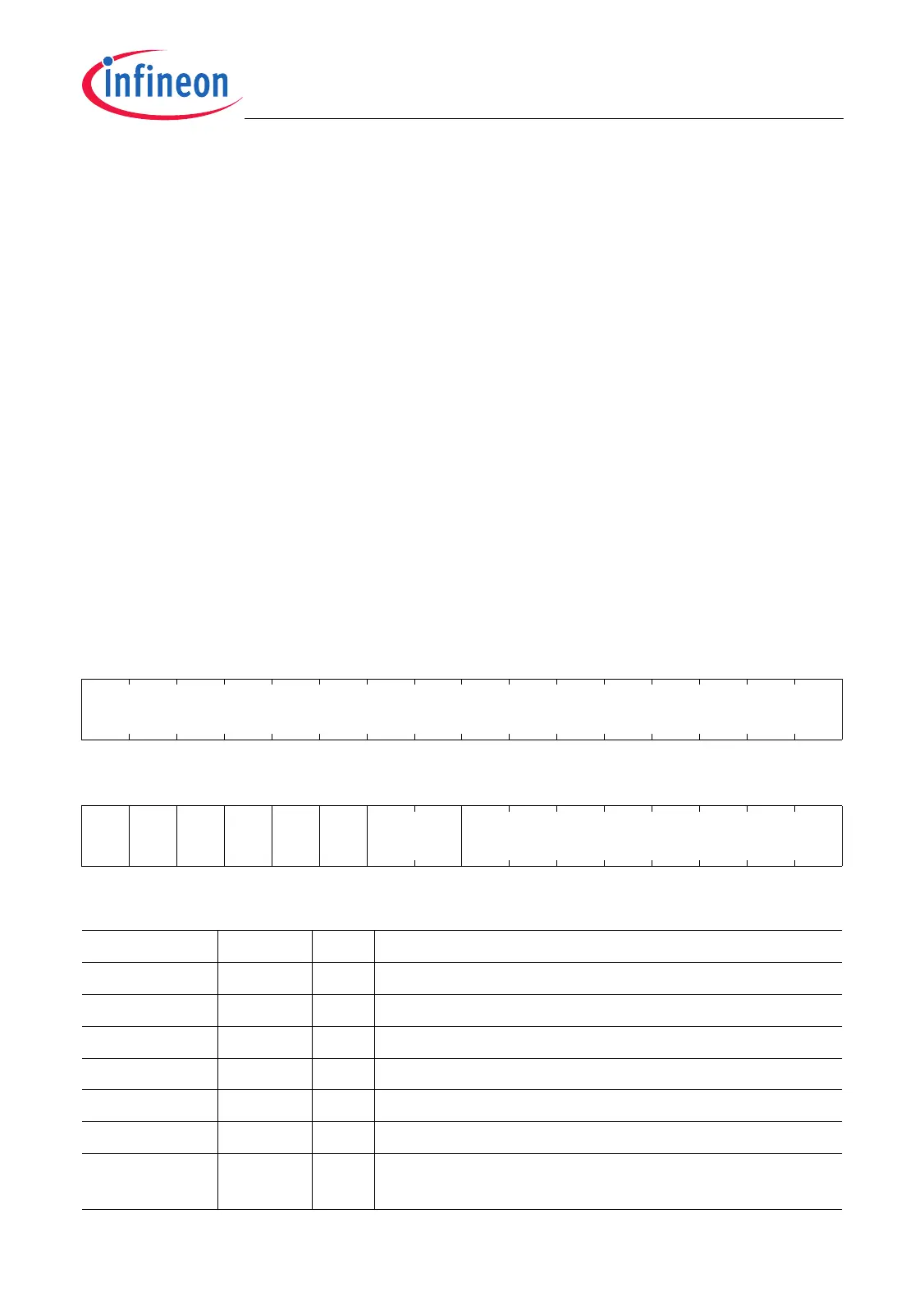

Field Bits Type Description

SRPN [7:0] rw Service Request Priority Number

TOS 10 rw Type of Service Control

SRE 12 rw Service Request Enable

SRR 13 rh Service Request Flag

CLRR 14 w Request Clear Bit

SETR 15 w Request Set Bit

0 [9:8], 11,

[31:16]

r Reserved

Read as 0; should be written with 0.

Loading...

Loading...