TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-49 V2.0, 2007-07

CPU, V2.0

2.7.2.2 Control Flow Instruction Timing

• Each instruction is single issued.

• All targets yield a full instruction in one access (not 16-bits of a 32-bit instruction).

• All code fetches take a single cycle.Timing is best case; no cache misses for context

operations, no pending stores.

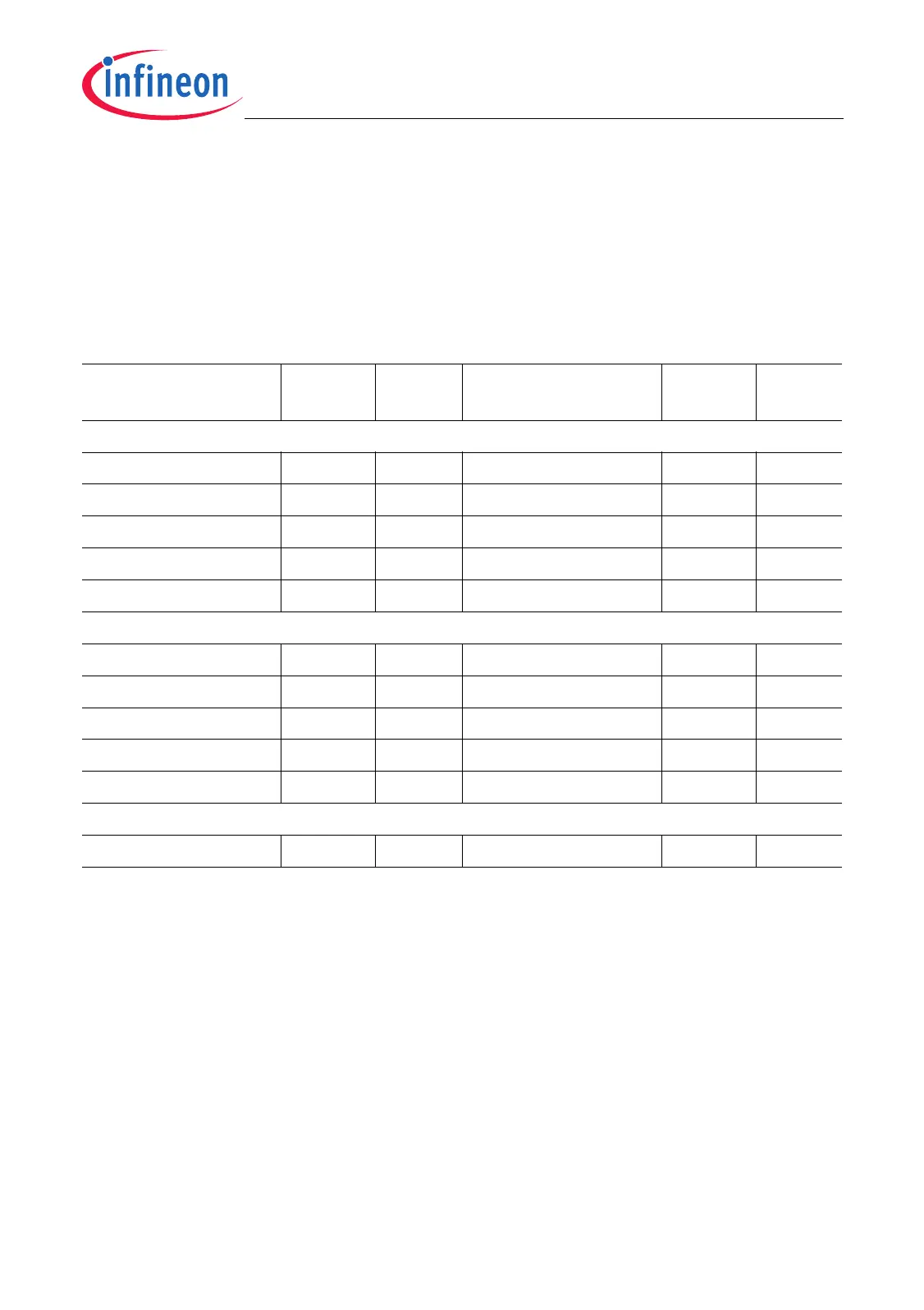

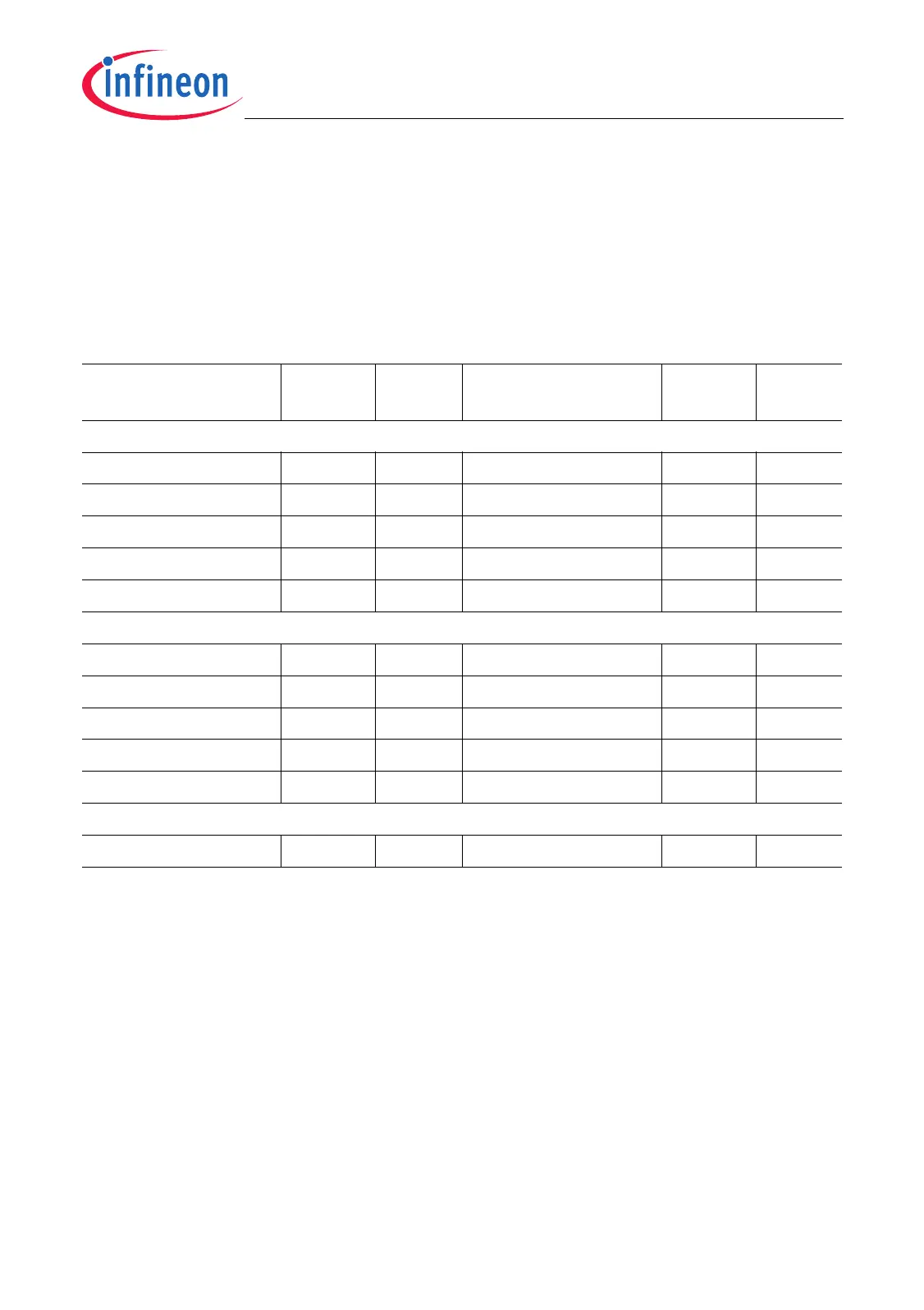

Table 2-15 Load/Store Control Flow Instruction Timing

Instruction Flow

Latency

Repeat

Rate

Instruction Flow

Latency

Repeat

Rate

Branch Instructions

J 22JLI 22

JA 22JEQ.A 1/2/3 1/2/3

JI 22JNE.A 1/2/3 1/2/3

JL 22JNZ.A 1/2/3 1/2/3

JLA 22JZ.A 1/2/3 1/2/3

CSA Instructions

CALL

1)

1) Latency of CSA related instructions varies according to preceding instruction and status of the shadow register

file. Average latency is ~2.7 cycles

2-5 2-5 SYSCALL

1)

–2-5

CALLA

1)

2-5 2-5 SVLCX

1)

–4-9

CALLI

1)

2-5 2-5 RSLCX

1)

–4

RET

1)

–2-5RFE

1)

–2-5

BISR

1)

–4-9RFM

2)

2) Not strictly a CSA operation, but retrieves from memory a subset of context information and changes control

flow in a similar manner.

––

Loop Instructions

LOOP

3)

3) First time encountered executed in LS pipeline: Flow latency = 2, Repeat rate = 2

Successive time executed in Loop Pipeline: Flow latency = 1: Repeat rate = 1 (nested up to 2 deep)

Last time encountered: Flow latency = 3: Repeat rate = 3

2/1/3 2/1/3 LOOPU

3)

2/1/3 2/1/3

Loading...

Loading...