TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-18 V2.0, 2007-07

CPU, V2.0

2.4.4.1 Implementation-specific Core Debug Registers

This section describes the implementation-specific Core Debug Registers which differ

from the description in the TriCore 1 Architecture Manual. These are:

• Trigger Event 0 Specifier Register

• Trigger Event 1 Specifier Register

• Software Breakpoint Service Request Control Register 0

The non-shaded areas in the register description define the implementation-specific

bits/bit fields.

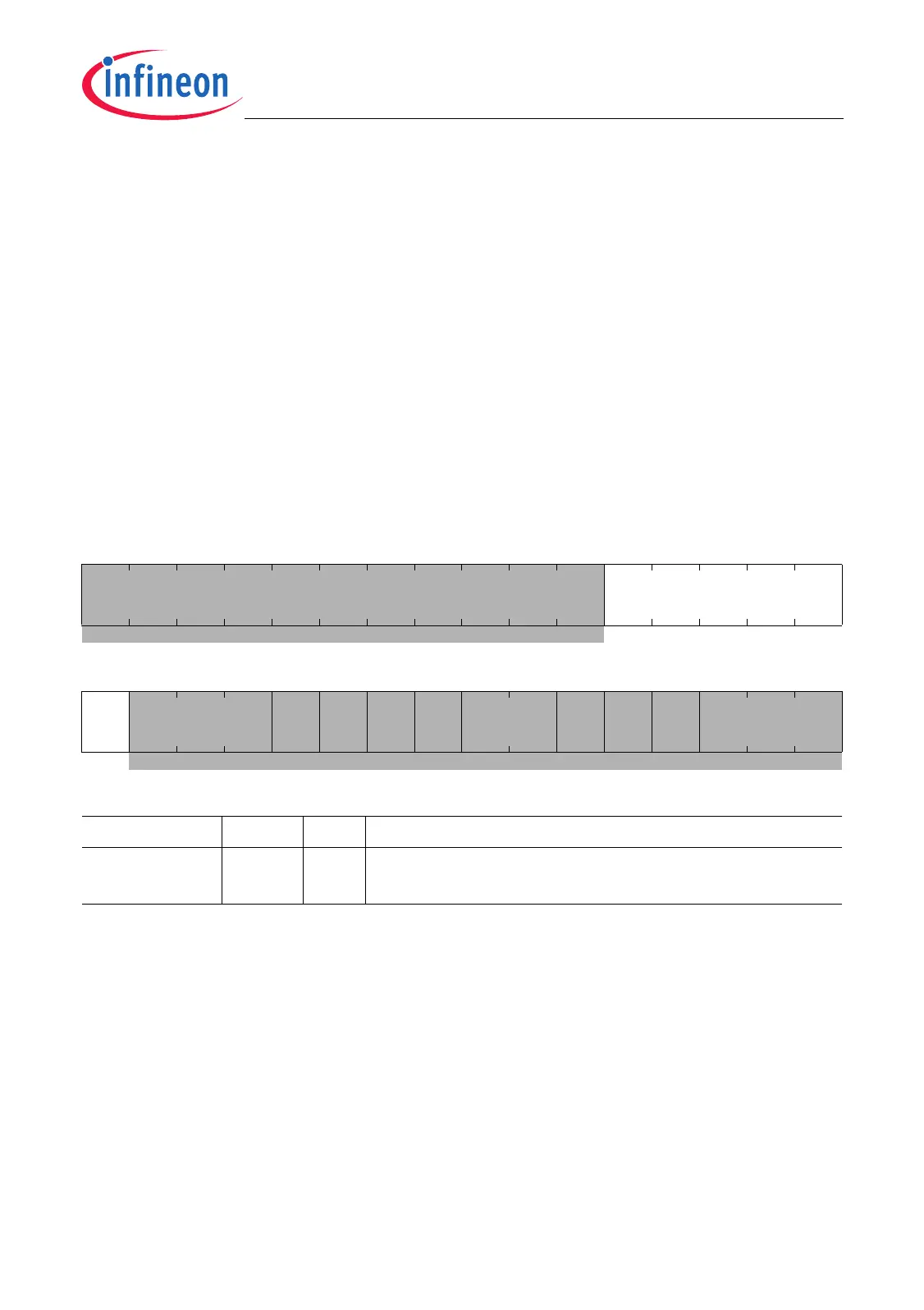

TR0EVT

Trigger Event 0 Specifier Register (F7E1 FD20

H

) Reset Value: 0000 0000

H

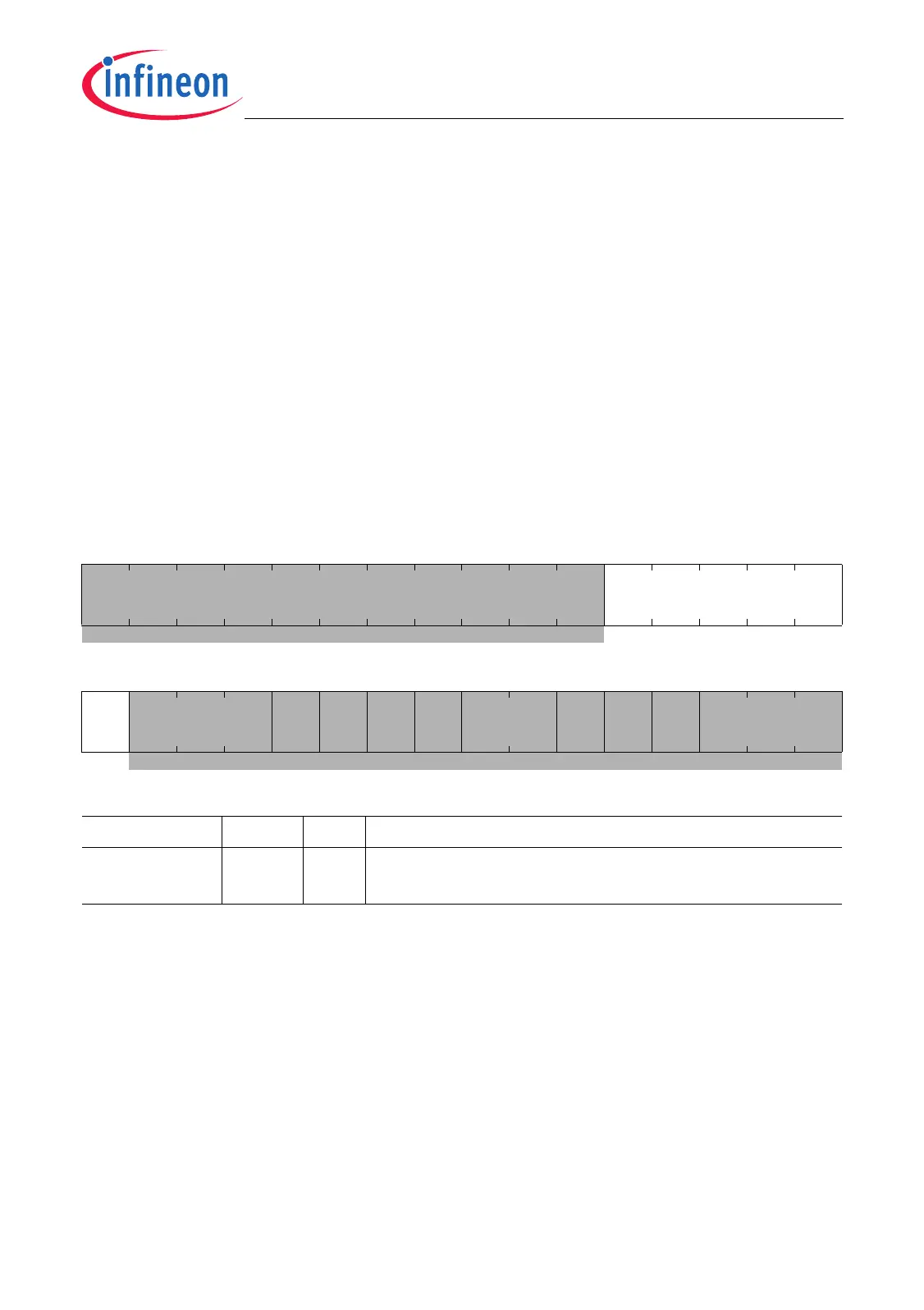

TR1EVT

Trigger Event 1 Specifier Register (F7E1 FD20

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

00

rr

1514131211109876543210

0 0

DU

_U

DU

_LR

DLR

_U

DLR

_LR

0

SU

SP

0 BBM EVTA

r r rw rw rw rw r rw r rw rw

Field Bits Type Description

0 [20:15] r Reserved

Read as 0; should be written with 0.

Loading...

Loading...