TC1796

System Units (Vol. 1 of 2)

Memory Maps

User’s Manual 9-19 V2.0, 2007-07

MemMaps, V2.0

9.5 Address Map of the Data Local Memory Bus (DLMB)

Table 9-4 shows the address map of as it is seen from the DLMB bus masters (DMI and

LFI Bridge).

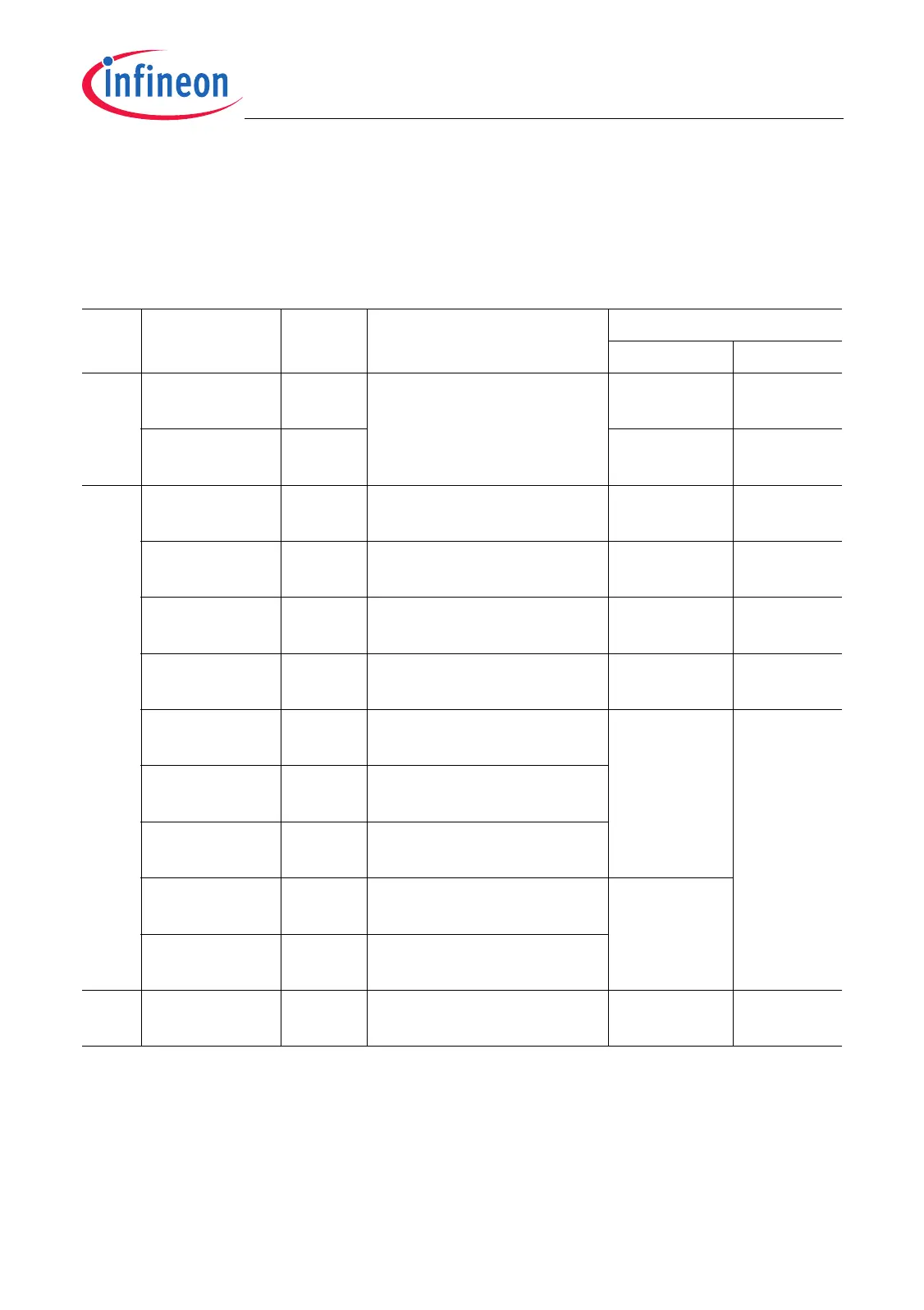

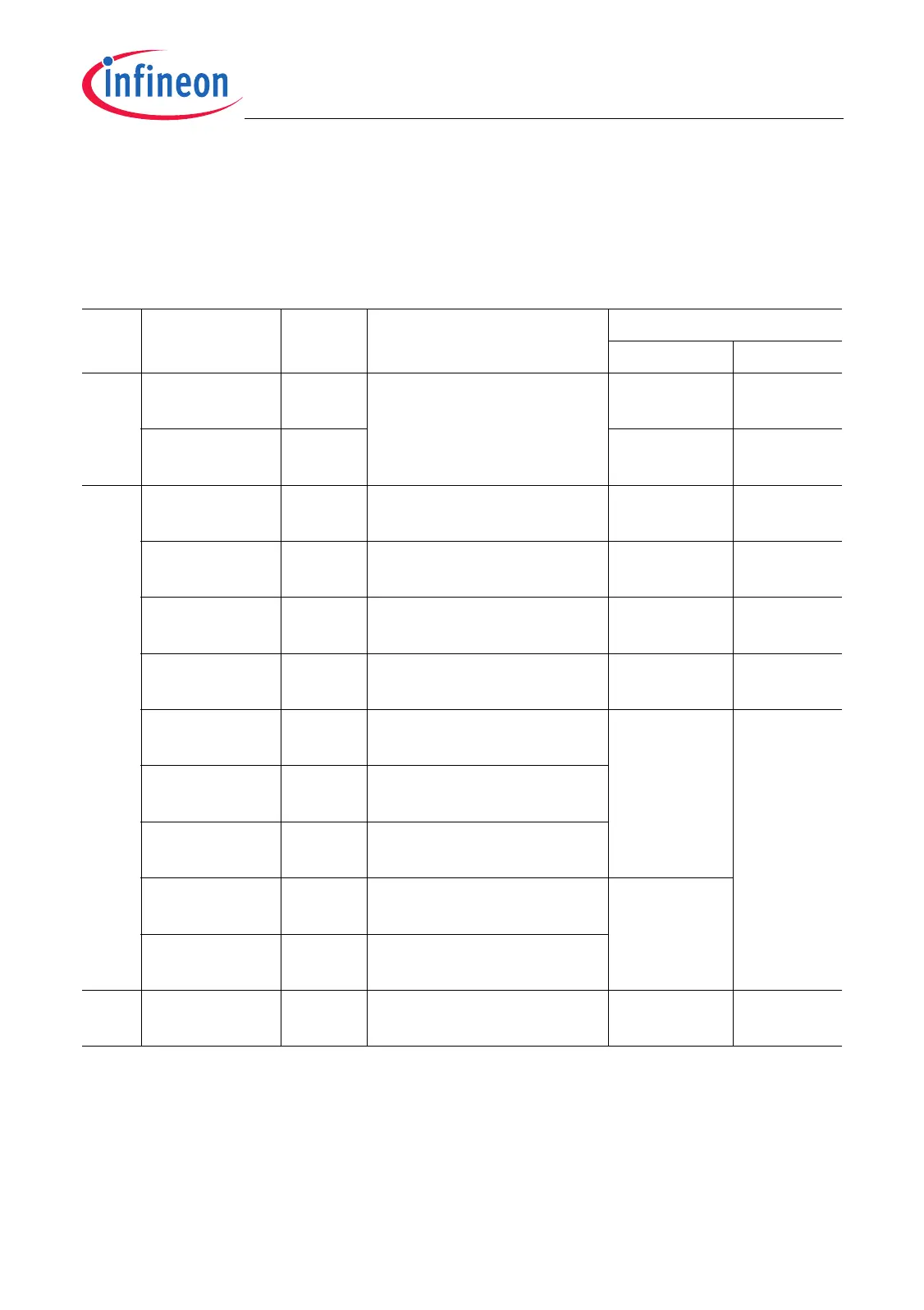

Table 9-5 DLMB Address Map

Seg-

ment

Addresses Size Description Action

Read Write

0-7

1)

0000 0000

H

-

0000 0007

H

8 byte Reserved (virtual address

space)

MPN Trap MPN Trap

0000 0008

H

-

7FFF FFFF

H

8 × 256

Mbyte

DLMBBET&

SPBBET

SPBBE

8

1)

8000 0000

H

-

801F FFFF

H

2 Mbyte Program Flash (PFLASH) access access

2)

8020 0000

H

-

807F FFFF

H

6 Mbyte Reserved PLMBBET &

DLMBBET

PLMBBE

8080 0000

H

-

8FDF FFFF

H

246

Mbyte

External EBU space EBU

access

EBU

access

8FE0 0000

H

-

8FE1 FFFF

H

128

Kbyte

Data Flash (DFLASH) access access

2)

8FE2 0000

H

-

8FEF FFFF

H

896

Kbyte

Reserved PLMBBET &

DLMBBET

PLMBBE

8FF0 0000

H

-

8FF7 FFFF

H

512

Kbyte

Reserved for TC1796

emulation device memory

8FF8 0000

H

-

8FFF BFFF

H

496

Kbyte

Reserved

8FFF C000

H

-

8FFF DFFF

H

8 Kbyte Boot ROM (BROM) access

8FFF E000

H

-

8FFF FFFF

H

8 Kbyte Test ROM (TROM)

9

1)

9000 0000

H

-

9FFF FFFF

H

256

Mbyte

Reserved DLMBBET &

SPBBET

SPBBE

Loading...

Loading...