TC1796

System Units (Vol. 1 of 2)

Clock System and Control

User’s Manual 3-12 V2.0, 2007-07

Clock, V2.0

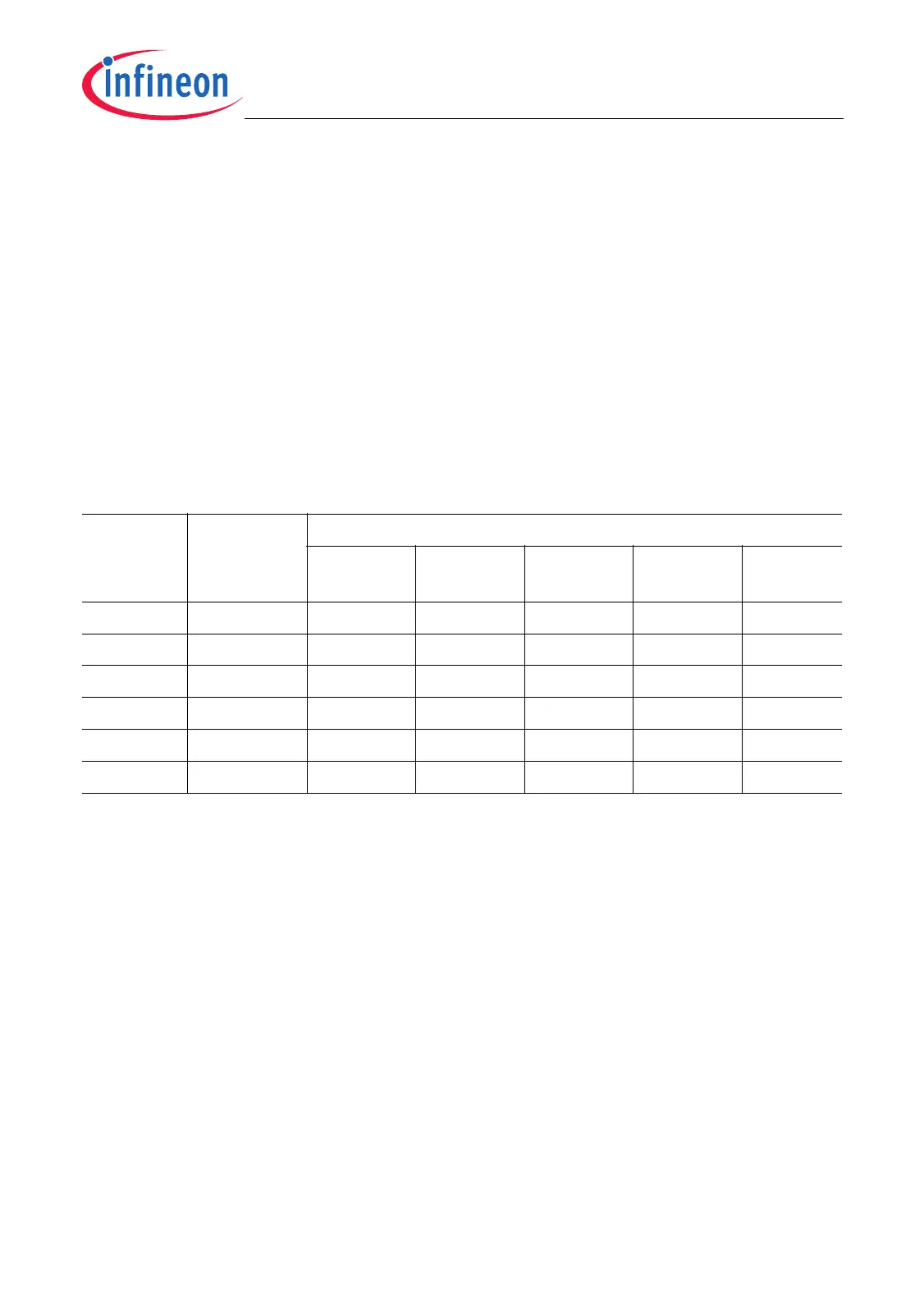

3.2.2.2 PLL Parameters

As shown in Equation (3.2) to Equation (3.3), the PLL operation depends on the setup

of up to four main PLL parameters: P-Divider, N-Divider, K-Divider, and VCO range

selection.

P-Divider

The P-Divider divides the oscillator clock f

OSC

by factor P for the PLL input clock f

P

.

Table 3-2 shows the P factor values of the P-Divider which are selected by programming

the PLL_CLC.PDIV bit field. It also lists the resulting f

P

frequency for some dedicated

values of f

OSC

but the complete range of 4 to 40 MHz can be applied and used for f

OSC

.

Note that the P-Divider factor is always PLL_CLC.PDIV+1.

Table 3-2 P-Divider Selections

PLL_CLC.

PDIV

P-Divider:

P=PDIV+1

Resulting f

P

Frequency (in MHz) for

f

OSC

=

4 MHz

f

OSC

=

10 MHz

f

OSC

=

20 MHz

f

OSC

=

30 MHz

f

OSC

=

40 MHz

0 1 4 10203040

1 2 2 5 10 15 20

2 3 1.33 3.33 6.67 10 13.3

… … ……………

6 7 0.57 1.43 2.857 4.286 5.7

7 8 0.5 1.25 2.5 3.75 5

Loading...

Loading...