TC1796

System Units (Vol. 1 of 2)

System Control Unit

User’s Manual 5-39 V2.0, 2007-07

SCU, V2.0

5.5.1 Parity Error Trap Registers

Additional details about the NMI handling of SRAM parity errors are described in section

“SRAM Parity Error NMI” on Page 14-26.

Note: SFR SCU_PETCR is Endinit-protected for write operations.

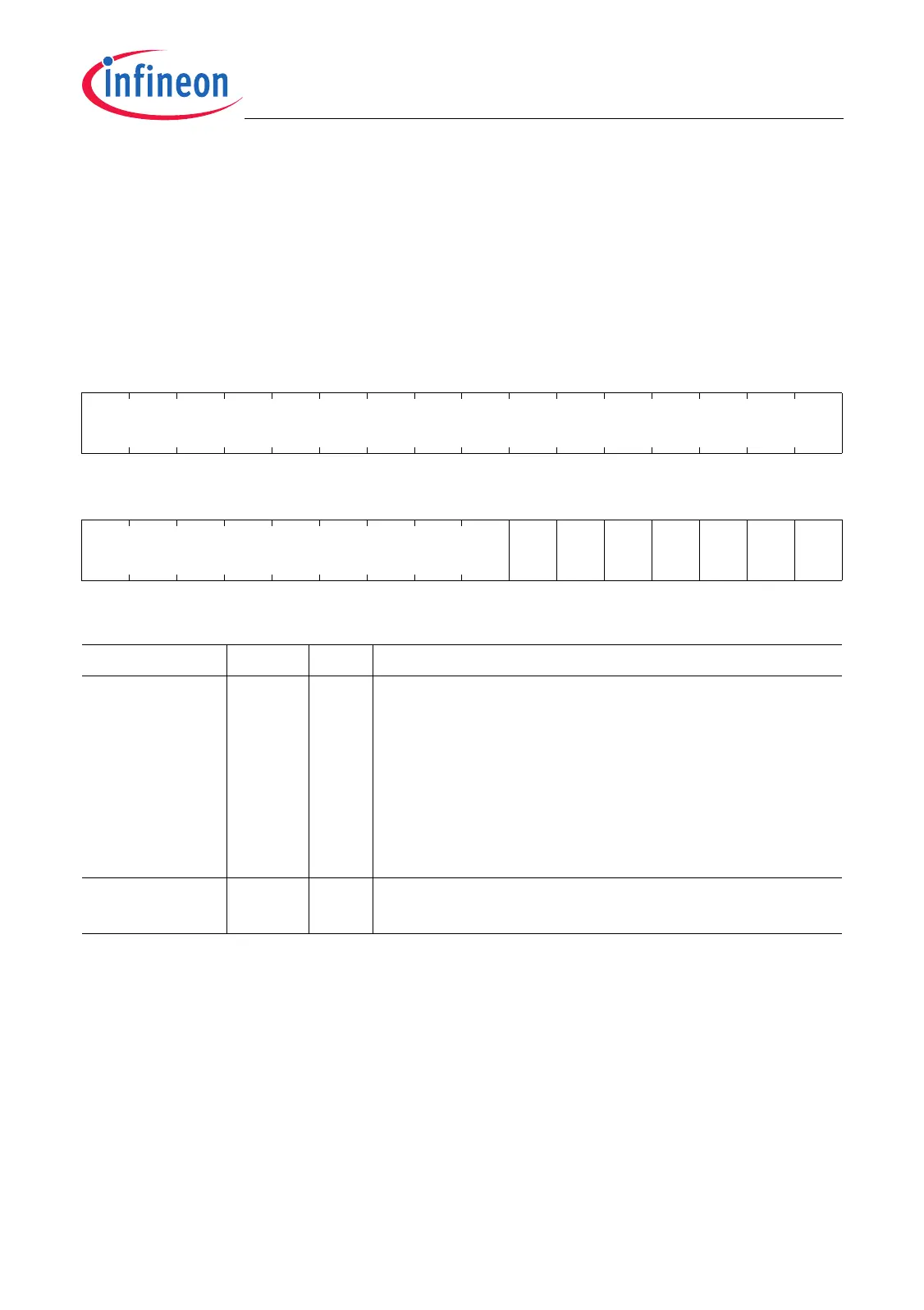

SCU_PETCR

SCU Parity Error Trap Control Register

(F00000D0

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0

PEN

6

PEN

5

PEN

4

PEN

3

PEN

2

PEN

1

PEN

0

r rwrwrwrwrwrwrw

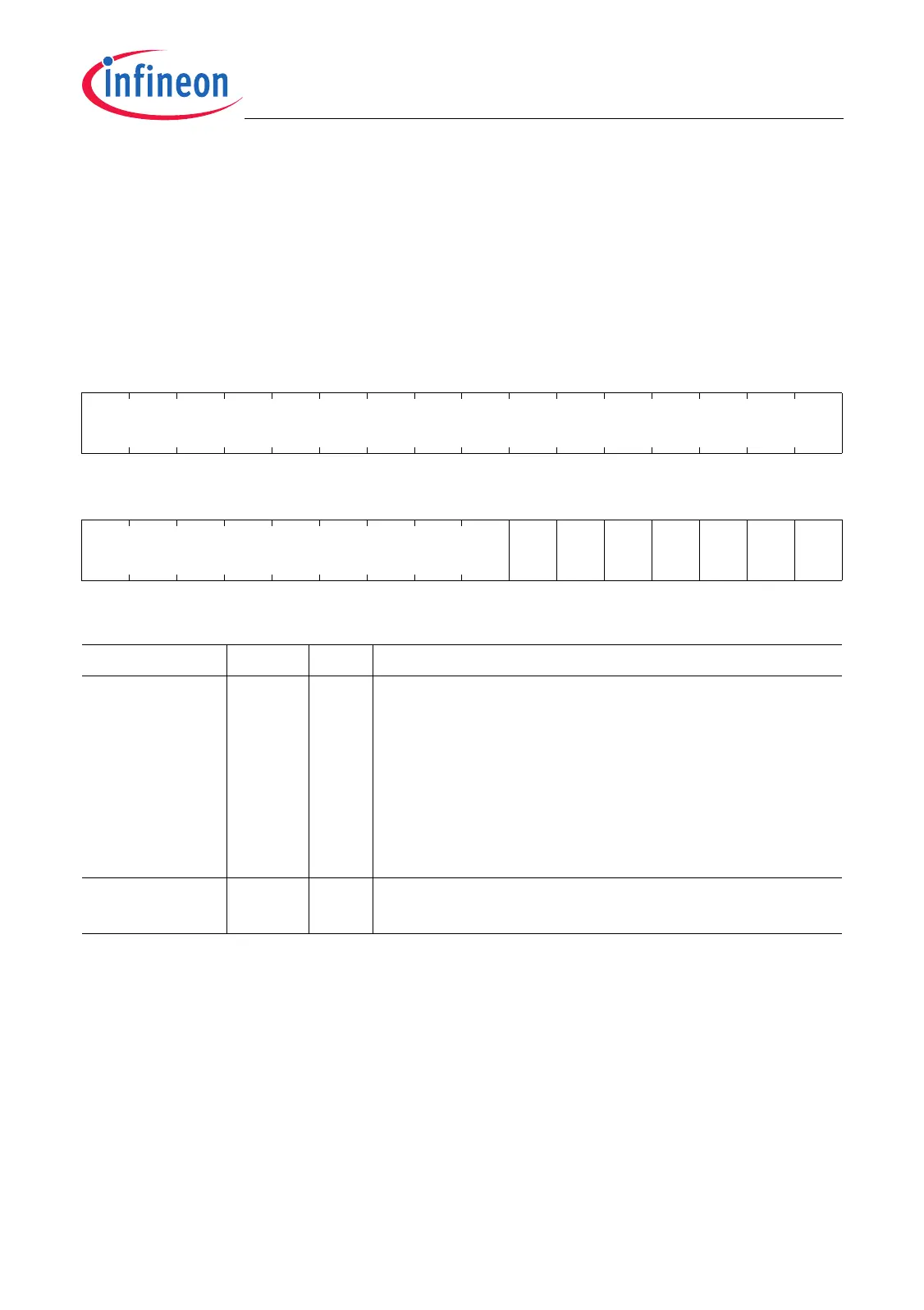

Field Bits Type Description

PENx

(x = 0-6)

xrwParity Error Trap Enable for SRAM Module x

These bits determine whether an NMI trap is

generated if a parity error is detected in the

associated SRAM memory module. The assignment

of the enable bits to the SRAM modules is defined in

Table 5-5.

0

B

NMI parity error trap is disabled.

1

B

NMI parity error trap is enabled.

0 [31:7] r Reserved

Read as 0; should be written with 0.

Loading...

Loading...