TC1796

System Units (Vol. 1 of 2)

Watchdog Timer

User’s Manual 16-31 V2.0, 2007-07

WDT, V2.0

16.6.2 Watchdog Timer Control Register 1

WDT_CON1 manages operation of the WDT. It includes the disable request and

frequency selection bits. It is ENDINIT-protected.

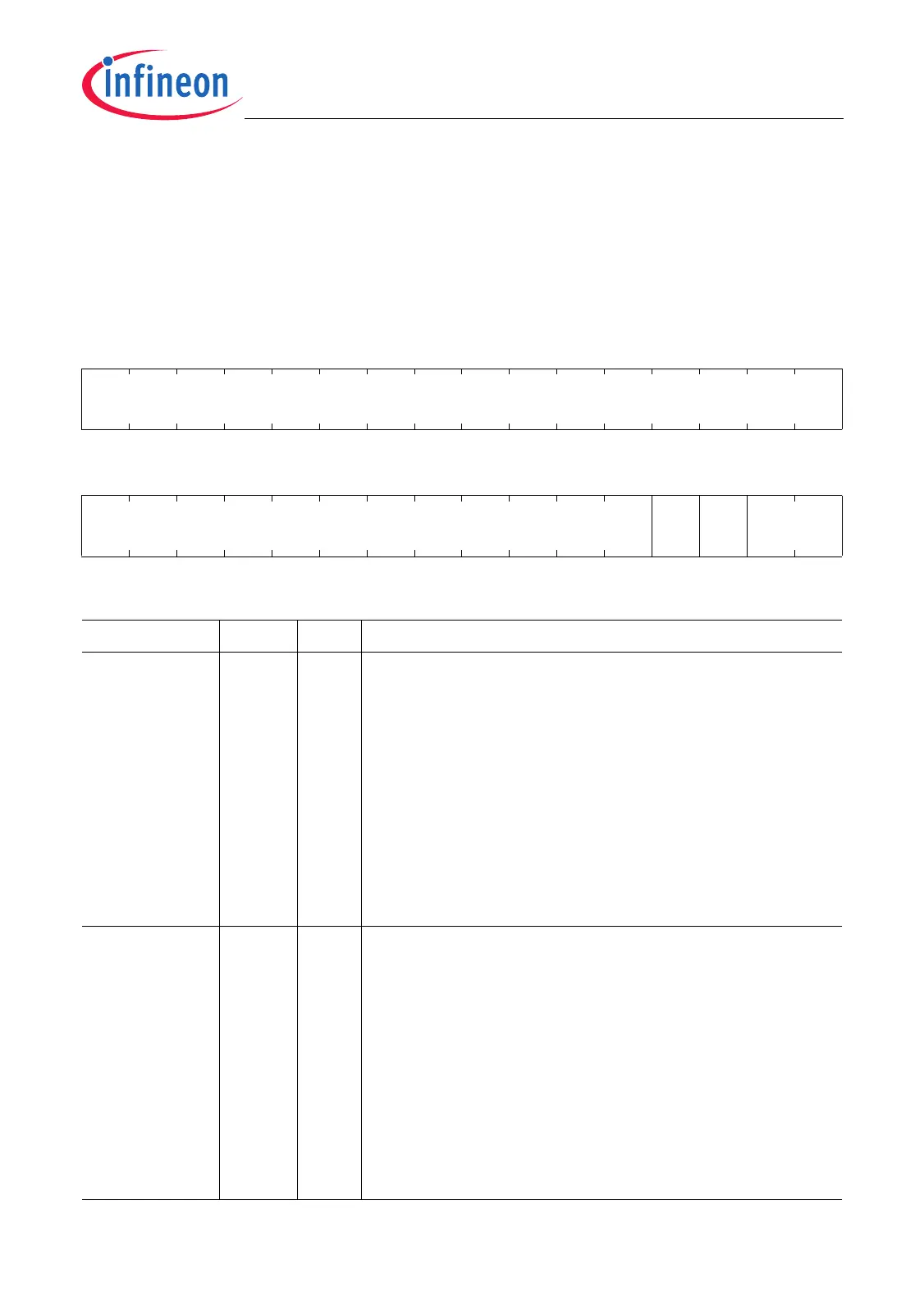

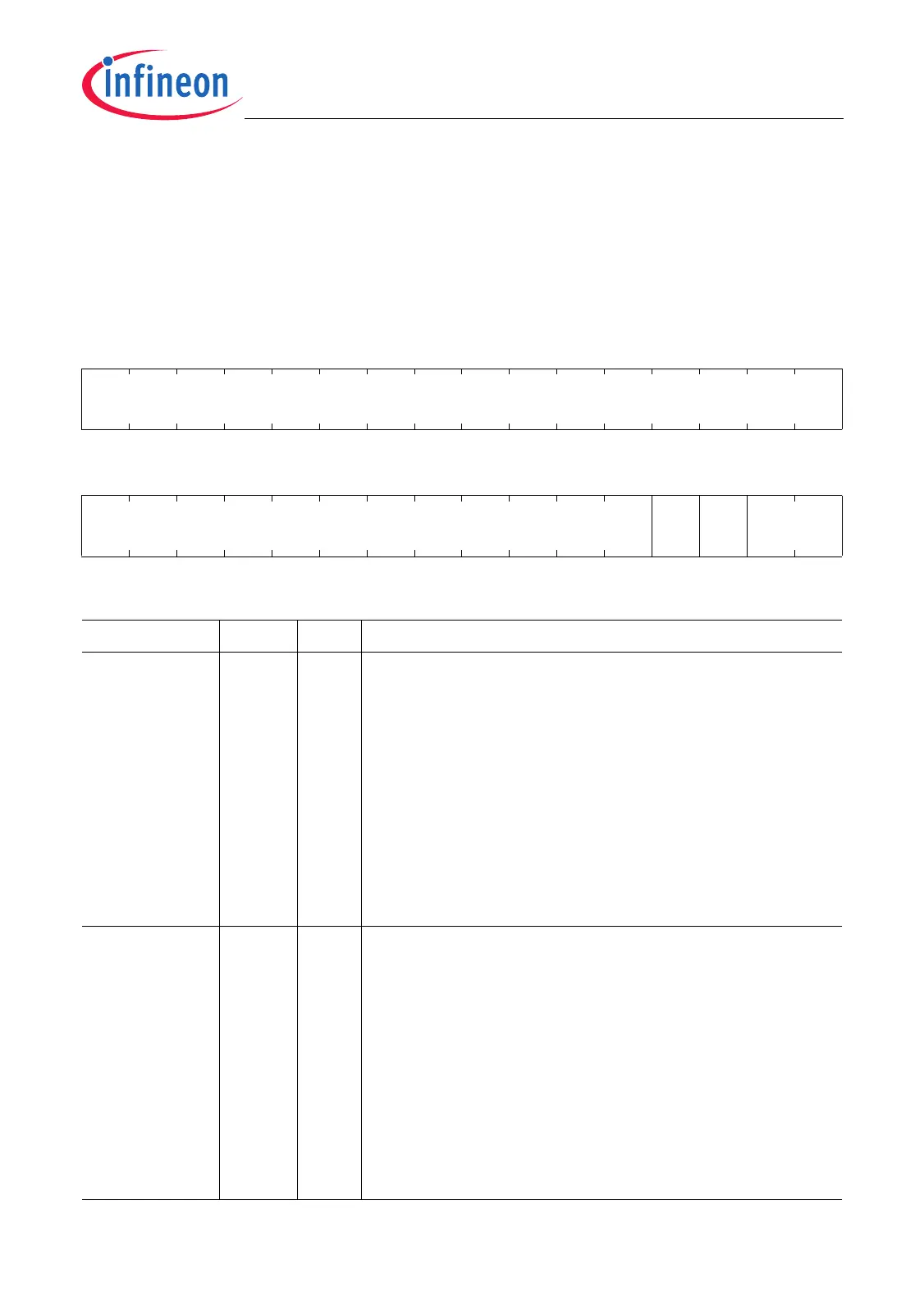

WDT_CON1

Watchdog Timer Control Register 1 (24

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0

WDT

DR

WDT

IR

0

rrwrwr

Field Bits Type Description

WDTIR 2rwWDT Input Frequency Request Control Bit

0

B

Request to set input frequency to

f

SYS

/16384.

1

B

Request to set input frequency to f

SYS

/256.

This bit can only be modified if WDT_CON0.ENDINIT

is set to 0. WDT_SR.WDTIS is updated by this bit only

when ENDINIT is set to 1 again. As long as ENDINIT

is left at 0, WDT_SR.WDTIS controls the current input

frequency of the WDT. When ENDINIT is set to 1

again, WDT_SR.WDTIS is updated with the state of

WDTIR.

WDTDR 3rwWatchdog Timer Disable Request Control Bit

0

B

Request to enable the WDT.

1

B

Request to disable the WDT.

This bit can only be modified if WDT_CON0.ENDINIT

is set to 0. WDT_SR.WDTDS is set to this bit’s value

when ENDINIT is set to 1 again. As long as ENDINIT

is left at 0, bit WDT_SR.WDTDS controls the current

enable/disable status of the WDT. When ENDINIT is

set to 1 again with a Valid Modify Access,

WDT_SR.WDTDS is updated with the state of

WDTDR.

Loading...

Loading...