TC1796

Peripheral Units (Vol. 2 of 2)

Micro Second Channel (MSC)

User’s Manual 21-34 V2.0, 2007-07

MSC, V2.0

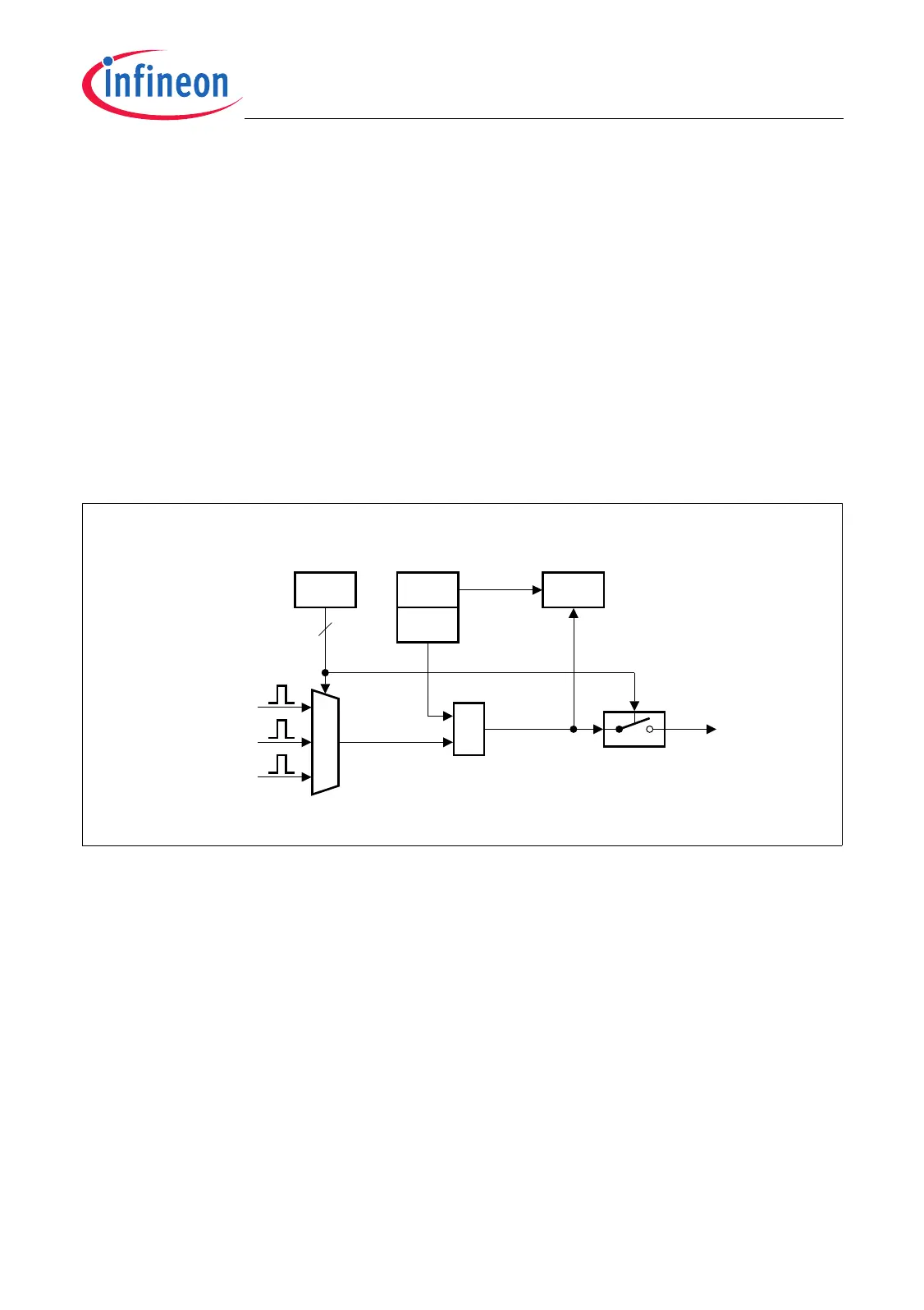

21.1.5.4 Receive Data Interrupt

Whenever the upstream channel receives data in registers UDx (x = 0-3), the MSC is

able to generate an interrupt. Three interrupt generation conditions can be selected for

the receive data interrupt:

• Each update of UDx (x = 0-3) generates a receive data interrupt.

• Each update of UDx (x = 0-3) generates a receive data interrupt when the updated

value is not equal 00

H

.

• Only an update of register UD3 generates a receive data interrupt.

The selection of the interrupt generation condition is controlled by bit field ICR.RDIE.

Setting ICR.RDIE = 0 disables the receive data interrupt in general. ISR.URDI is the

interrupt status flag that can be set or cleared when writing bits ISC.SRDI or ISC.CRDI

with a 1.

Figure 21-26 Receive Data Interrupt Control

MCA05820_mod

URDI

ISR

Data Frame

Interrupt

(to Int. Comp.)

EDI

Set

Software

Clear

RDIE = 00

ISC

SURDI

CURDI

≥1

Software

Set

Hardware

Set

RDIE

ICR

01

10

11

2

Data is received and

not equal 00

Data is received

Data is received in UD 3

H

Loading...

Loading...