TC1796

System Units (Vol. 1 of 2)

On-Chip Debug Support

User’s Manual 17-5 V2.0, 2007-07

OCDS, V2.0

– Breaks on data/address

Two precise data/address values or one data/address range

No break before make possible (due to pipelined architecture)

– Combinations of the above break conditions

• Real-time features

– Read and write of memory/registers quasi-concurrently, with minimum intrusion

(stealing bus cycles by Cerberus).

– High priority requests can still be serviced when the core is in emulation mode, by

interrupting the monitor program.

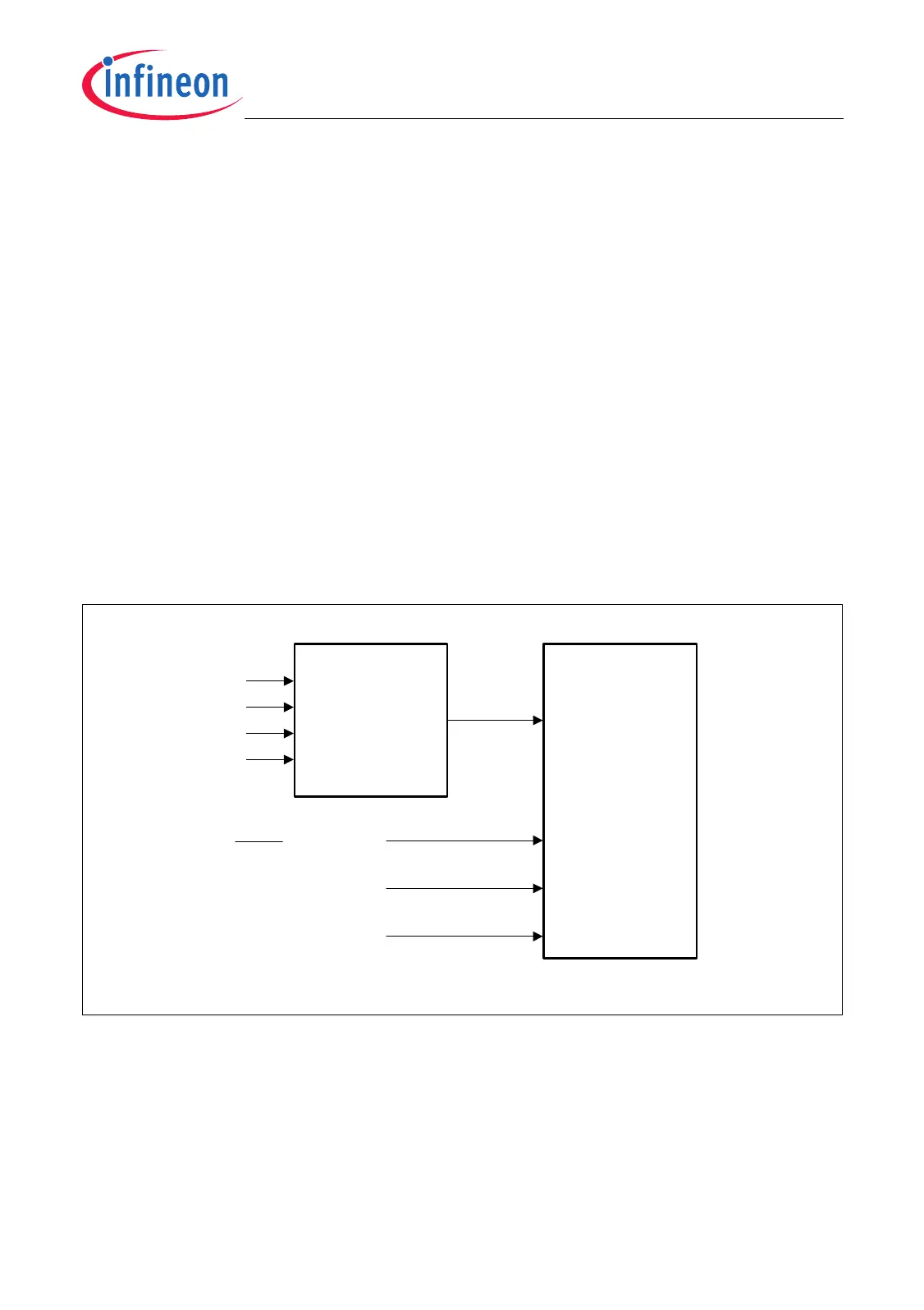

17.2.1.1 Basic Concept

The TriCore CPU in the TC1796 provides OCDS with the following two basic parts:

• Debug Event Trigger Generation

• Debug Event Trigger Processing

The first part controls the generation of debug events, and the second part controls what

actions are taken when a debug event is generated.

Figure 17-3 Basic TriCore Debug Concept

MCA05758

Debug

Event

Generation

Debug Triggers

Debug

Event

Processing

Ext. Break Input

(BRKIN)

Execution of the

DEBUG Instruction

Execution of MTCR /

MFCR Instruction

Loading...

Loading...