TC1796

System Units (Vol. 1 of 2)

Clock System and Control

User’s Manual 3-41 V2.0, 2007-07

Clock, V2.0

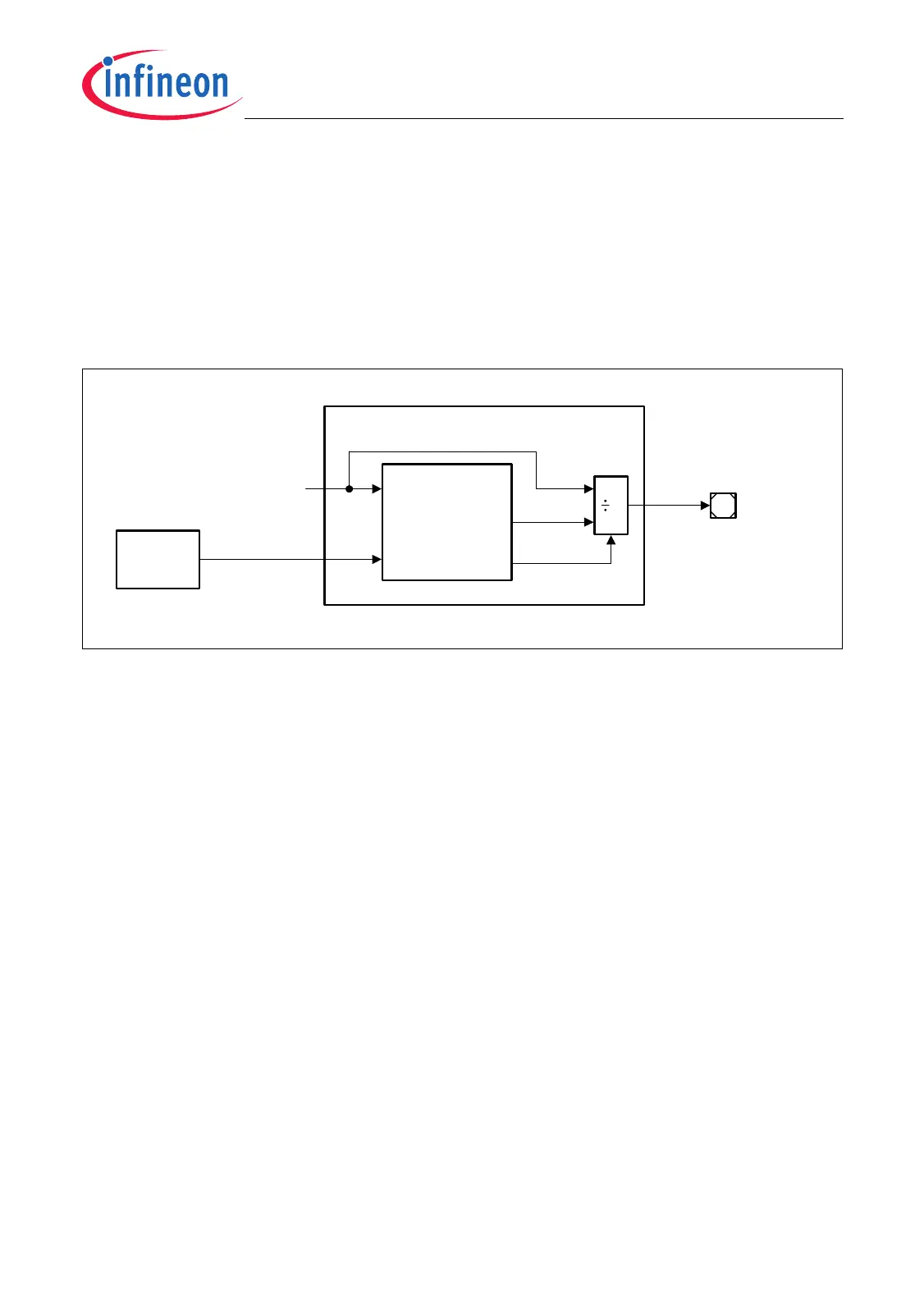

3.4 System Clock Output Control

The System Clock SYSCLK (alternate function of GPIO port line P1.12) is generated by

a fractional divider block with a subsequent divide-by-2 stage (see Figure 3-10). This

allows the SYSCLK frequency to be highly independent from the system frequency.

Furthermore, the SYSCLK signal has duty cycle of 50% (with a small period jitter). After

reset, SYSCLK is at low level when the Reset External Divider signal is at 1 (fractional

divider stopped).

Figure 3-10 SYSCLK Generation

In normal divider mode, f

SYSCLK

has a duty cycle of approximately 50%. The output

frequency of f

SYSCLK

in normal divider mode is defined according to the following formula:

, with n = 1024 - STEP (3.7)

In fractional divider mode, f

OUT

is derived from the input clock f

IN

by division of a fraction

of n/1024 for any value of n from 0 to 1023. In general, the fractional divider mode makes

it possible to program the average output clock frequency with a higher accuracy than in

normal divider mode. Note that in fractional divider mode, the clock f

OUT

can have a

maximum period jitter of one f

IN

clock period (f

SYSCLK

has a maximum period jitter of one

half f

IN

clock period).

The output frequency of f

SYSCLK

in fractional divider mode is defined according to the

following formula:

, with n = 0-1023 (3.8)

MCA05608

Fractional

Divider

Register

SCU_SCLKFDR

SYSCLK Generation

f

SYSCLK

P1.12 /

SYSCLK

2

f

OUT

ECEN

Enable

f

IN

Reset Ext.

f

SYS

MultiCAN

Module

CAN_INT_O15

Divider

f

SYSCLK

f

OUT

2⁄

f

SYS

2n×

-------------------

==

SYSCLK

f

OUT

2⁄ f

SYS

n

21024×

----------------------------------

×==

Loading...

Loading...