TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual 22-125 V2.0, 2007-07

MultiCAN, V2.0

Therefore, the first entry read after BCE is STPTR0 in order to obtain the address where

TME1 is located.

22.6.2.1 Scheduler Entry Types

The scheduler instruction entries are located after the time mark entry. The time mark

entry determines the behavior of the TTCAN when the next time mark is reached. The

scheduler instructions after the time mark entry are valid for the time mark they follow.

The scheduler control reads the time mark entry and sets up the compare action

(compare between the new time mark with the cycle time). Then, the scheduler reads

the following instructions and sets up the transfer behavior of the TTCAN node. The

scheduler stops reading from the scheduler memory when a new time mark entry is

found.

The transfer behavior set up can change with each scheduler instruction. There is no

built-in consistency check for scheduler instructions. Previously read scheduler

instructions can be overwritten by subsequent ones. With each time mark, the settings

are cleared and must be set up by new scheduler instructions (if desired).

The complete scheduler information must be finished with a basic cycle end entry that

fixes the value for the watch trigger event.

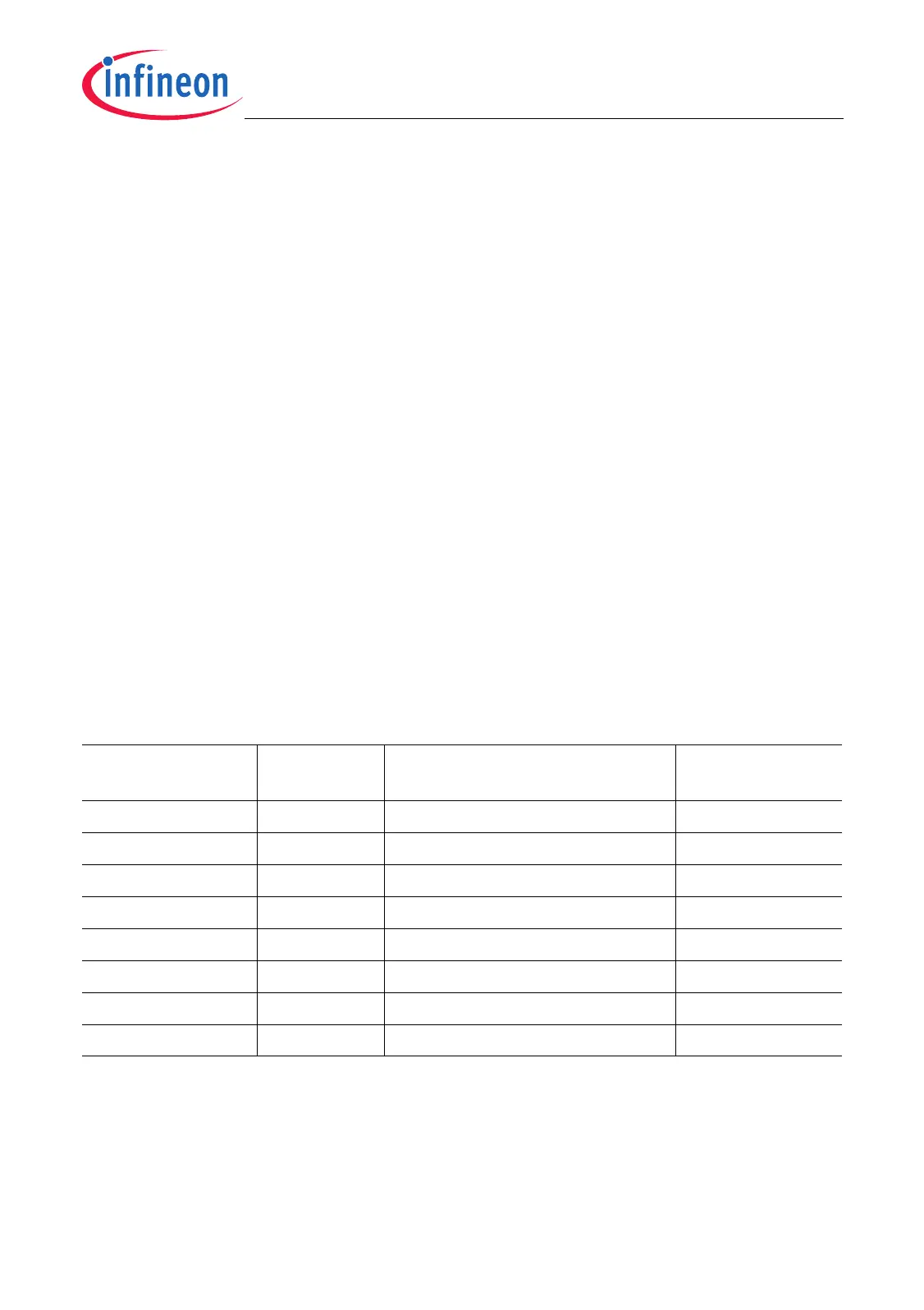

Each entry in the scheduler memory contains a 4-bit wide code field that determines the

type of the entry. The possible scheduler memory entry types are listed in Table 22-13.

The general transmit trigger control for the message objects to be transmitted when a

time mark is reached is performed by the message objects themselves. In order to

increase the flexibility, the result of the acceptance filtering done with the message

objects can be overruled by control entries. A reference message can be transmitted

only when the CAN node is enabled as time master.

Table 22-13 Scheduler Memory Entry Types

Entry Code EC

Bits [31:28]

Short Name Entry Type Defined at

0001

B

TME Time mark entry see Page 22-126

0010

B

ICE Interrupt control entry see Page 22-129

0011

B

ARBE Arbitration entry see Page 22-131

0100

B

TCE Transmit control entry see Page 22-133

0101

B

RCE Receive control entry see Page 22-136

0110

B

RME Reference message entry see Page 22-138

0111

B

BCE Basic cycle end entry see Page 22-140

other combinations EOS End of scheduler memory entry see Page 22-141

Loading...

Loading...