TC1796

System Units (Vol. 1 of 2)

Peripheral Control Processor (PCP)

User’s Manual 11-61 V2.0, 2007-07

PCP, V2.0

contents of the register are updated whenever there is a debug or an error event

detected (i.e. all status/error bits, other than the bit representing the last PCP

error/debug event, are cleared). This register therefore only provides a record of

the last error/debug event encountered. The only way to clear this register is to

reset the PCP.

11.10.5 PCP Interrupt Control Register, PCP_ICR

This register controls the operation of the PCP Interrupt Control Unit (PICU).

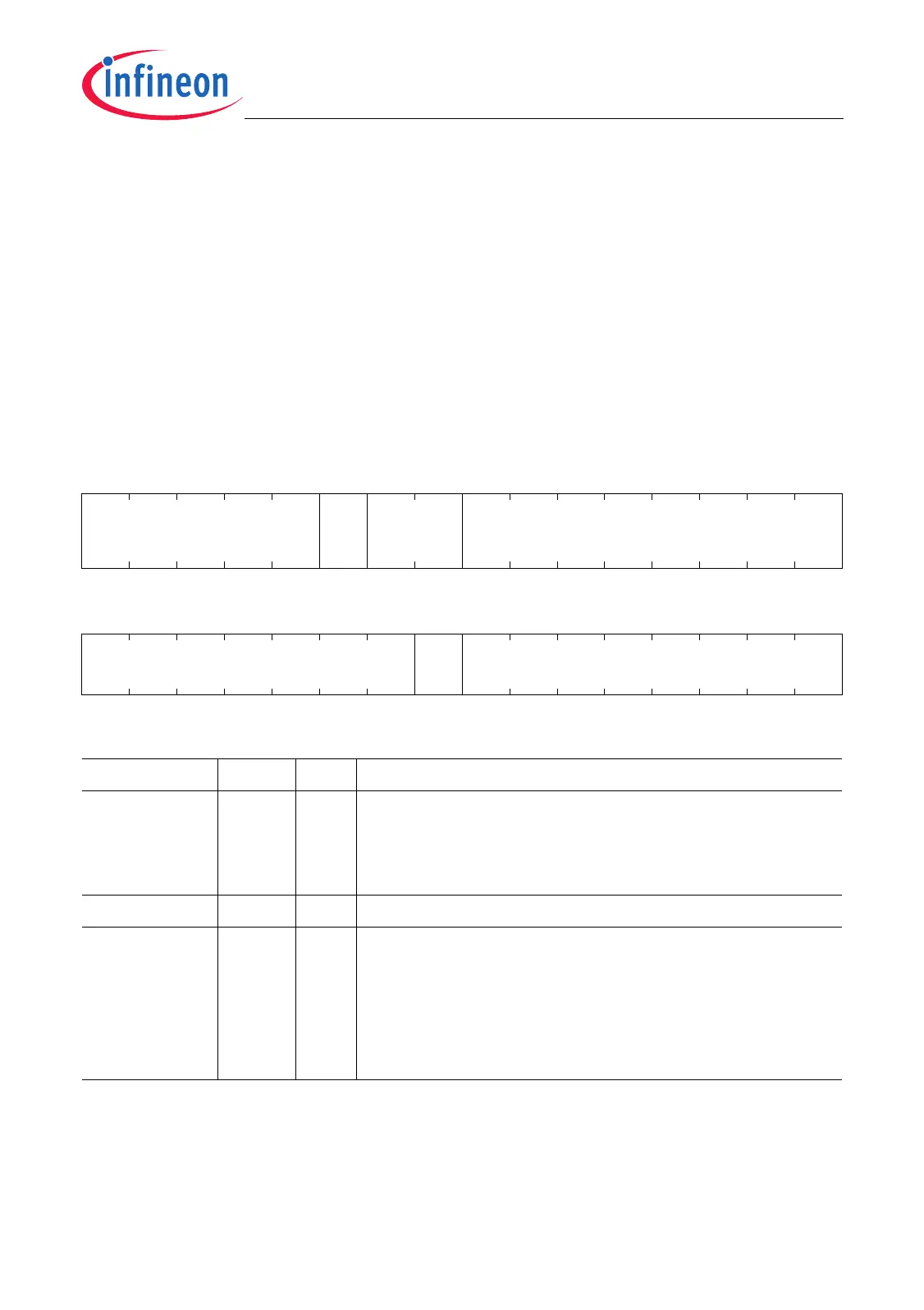

PCP_ICR

PCP Interrupt Control Register (20

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

P

ONE

CYC

PARBCYC PIPN

rrwrw rh

1514131211109876543210

0 IE CPPN

rrh rh

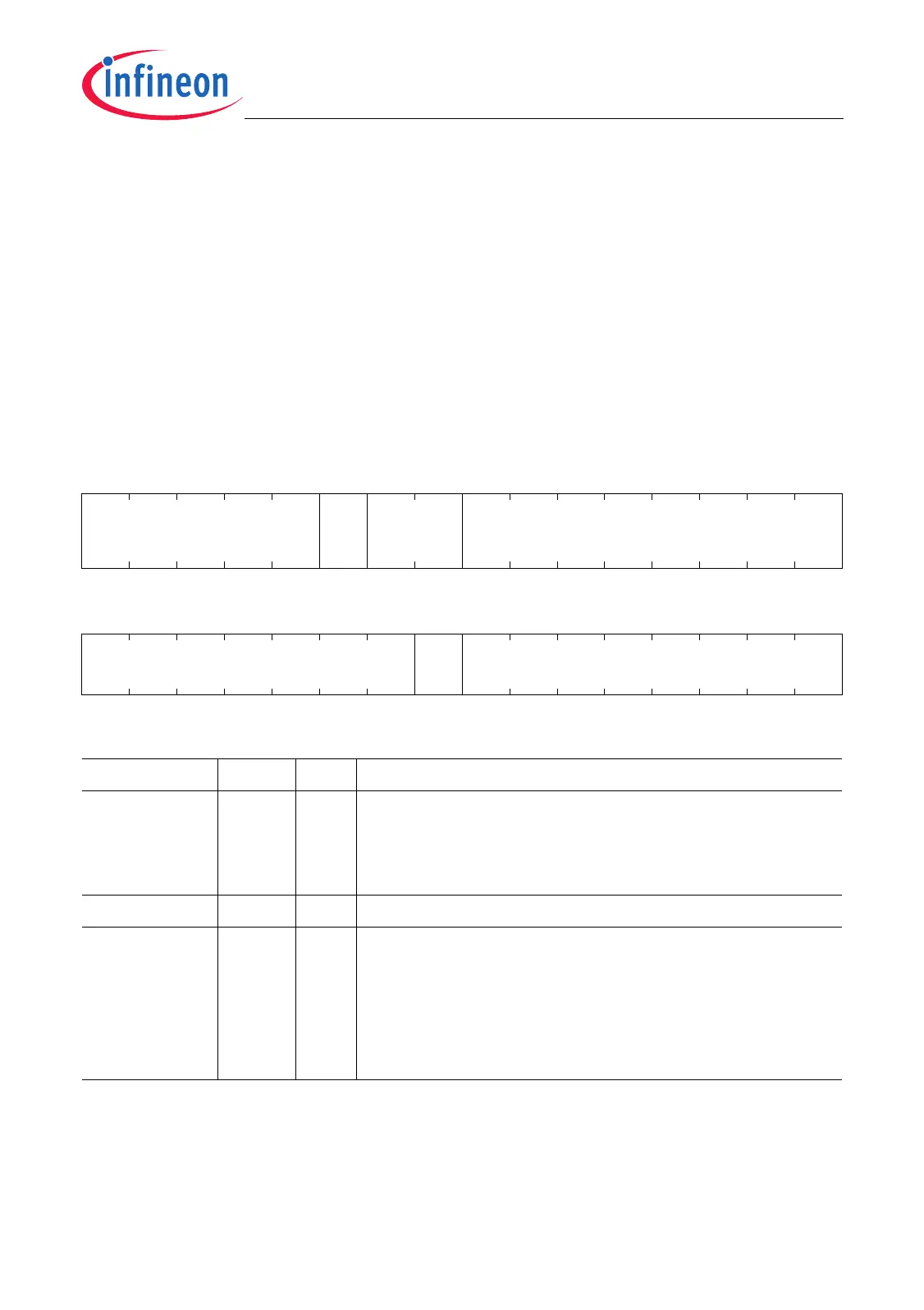

Field Bits Type Description

CPPN [7:0] rh Current PCP Priority Number

This field indicates the current priority level of the PCP

and is automatically updated by hardware on entry into

an interrupt service routine.

IE 8rhReserved

PIPN [23:16] rh Pending Interrupt Priority Number

This read-only field is updated by the PICU at the end

of each arbitration process, and indicates the priority

number of a pending request. PIPN is set to 00

H

when

no request is pending and at the beginning of a new

arbitration process.

Loading...

Loading...