TC1796

Peripheral Units (Vol. 2 of 2)

Micro Link Interface (MLI)

User’s Manual 23-22 V2.0, 2007-07

MLI, V2.0

too. This check is used as life-sign of the receiver and the MLI transmitter can detect

whether the receiver is able to react in-time to the transmitter actions (see also

Chapter 23.1.3.4).

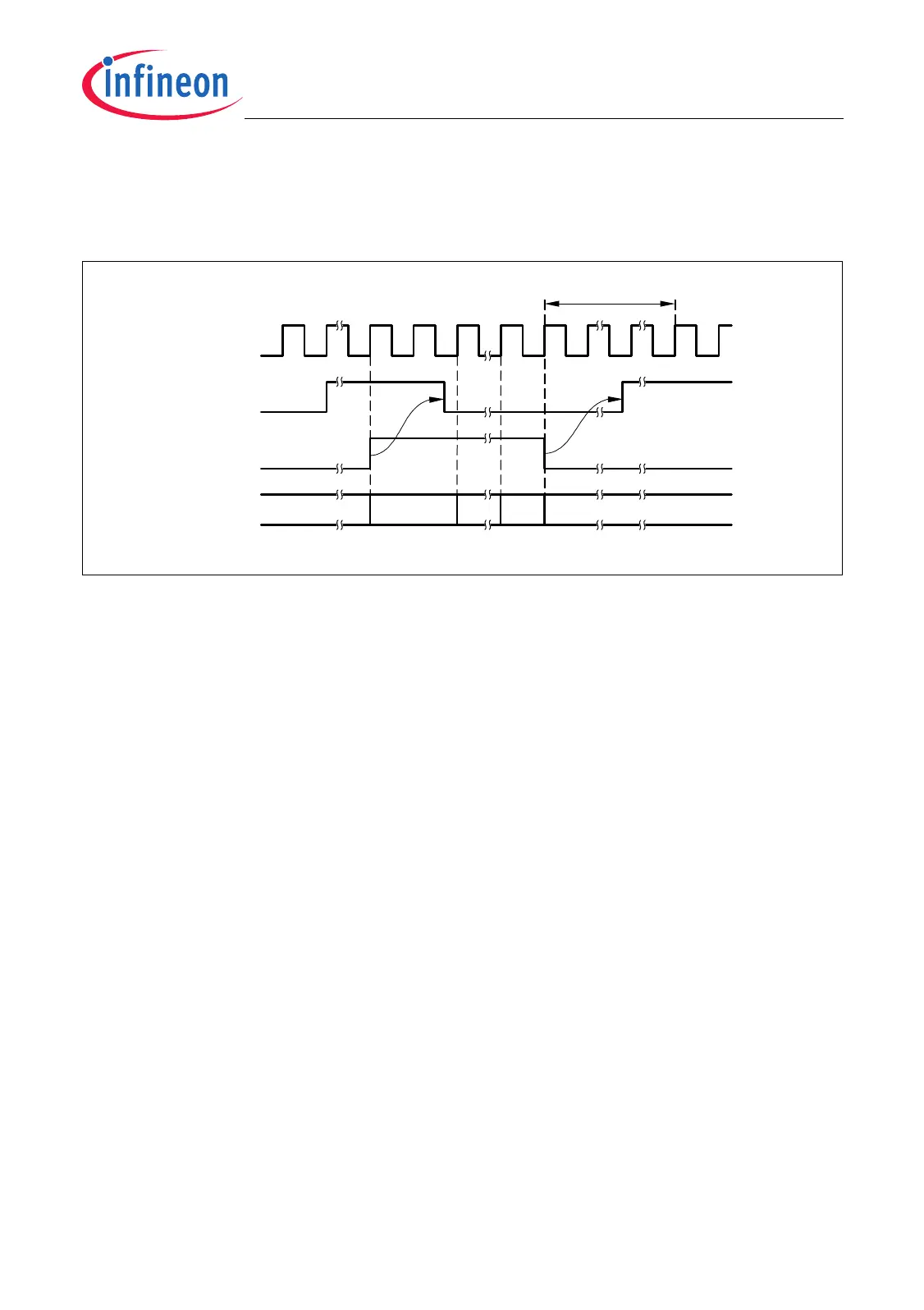

Figure 23-17 MLI Handshake without Error Indication

23.1.3.3 Ready Delay Time

In order to support significant propagation delays, the handshake signal TREADY is

evaluated with respect to TVALID and TCLK in an time interval called Ready Delay Time

after the end of the frame (see Figure 23-17). The length of the Ready Delay Time is

programmable, defining the size of the time interval.

When a transmission is finished (RVALID becomes 0), the MLI receiver checks the

received frame for correct reception (parity error). If no parity error has been detected,

the MLI receiver asserts its RREADY signal again to 1 to indicate the correct reception

with the next falling edge of RCLK. The MLI transmitter checks its TREADY input with

each rising edge of TCLK after TVALID has become 0 and increments a counter. This

counter is started from 0 at the end of a frame transmission (TVALID becomes 0) and

counts TCLK periods (Ready Delay Time Counter). If the condition TREADY = 1 is

detected before the programmed Ready Delay Time has elapsed, the MLI receiver has

indicated a frame reception without parity error to the MLI transmitter. In this case, a new

frame transmission can be started. The transfer handshake signalling without a parity

error indication is shown in Figure 23-17.

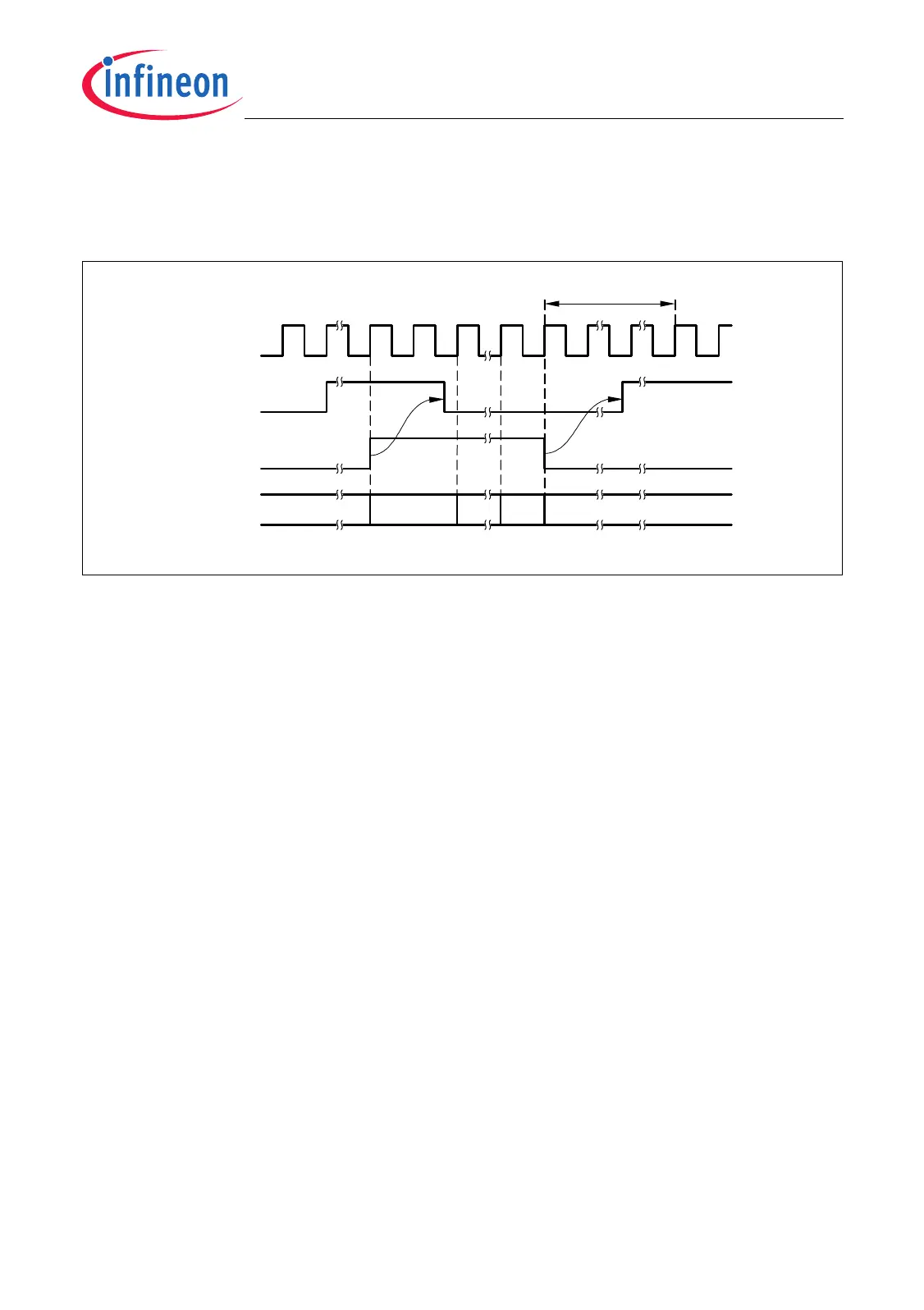

Figure 23-18 shows the transfer handshake if a parity error condition has been detected

by the MLI receiver and indicated to the MLI transmitter. In this case, the receiver waits

a programmable number of RCLK clock cycles before setting RREADY to 1. If the

TREADY = 1 condition is detected by the transmitter after the ready delay has elapsed,

a parity error has been indicated by the MLI receiver. In this case, it is assumed that the

MLI receiver has detected a frame with a parity error and has discarded the frame. The

MCT05874_mod

TVALID

TDATA

TREADY

TCLK

Ready Delay Time

PFC

Loading...

Loading...