TC1796

System Units (Vol. 1 of 2)

General Purpose I/O Ports and Peripheral I/O Lines

User’s Manual 10-37 V2.0, 2007-07

Ports, V2.0

10.5.3 Port 2 Registers

The following registers are available on Port 2:

Note: The complete address map of Port 2 is described in Table 18-11 on Page 18-24

of this TC1796 System Units (Vol. 1 of 2) User’s Manual.

10.5.3.1 Port 2 Output Register

The basic P2_OUT register functionality is described on Page 10-13. Port lines P2.[1:0]

are not connected to port lines. Therefore, reading the P2_OUT bits P[1:0] returns the

value that was last written (0 after reset). These bits can be also set/cleared by the

corresponding P2_OMR bits.

10.5.3.2 Port 2 Output Modification Register

The basic P2_OMR register functionality is described on Page 10-14. However, port

lines P2.0 and P2.1 are not available. Therefore, the P2_OMR bits PS[1:0] and PR[1:0]

have no direct effect on port lines but only on register bits P2_OUT.P[1:0].

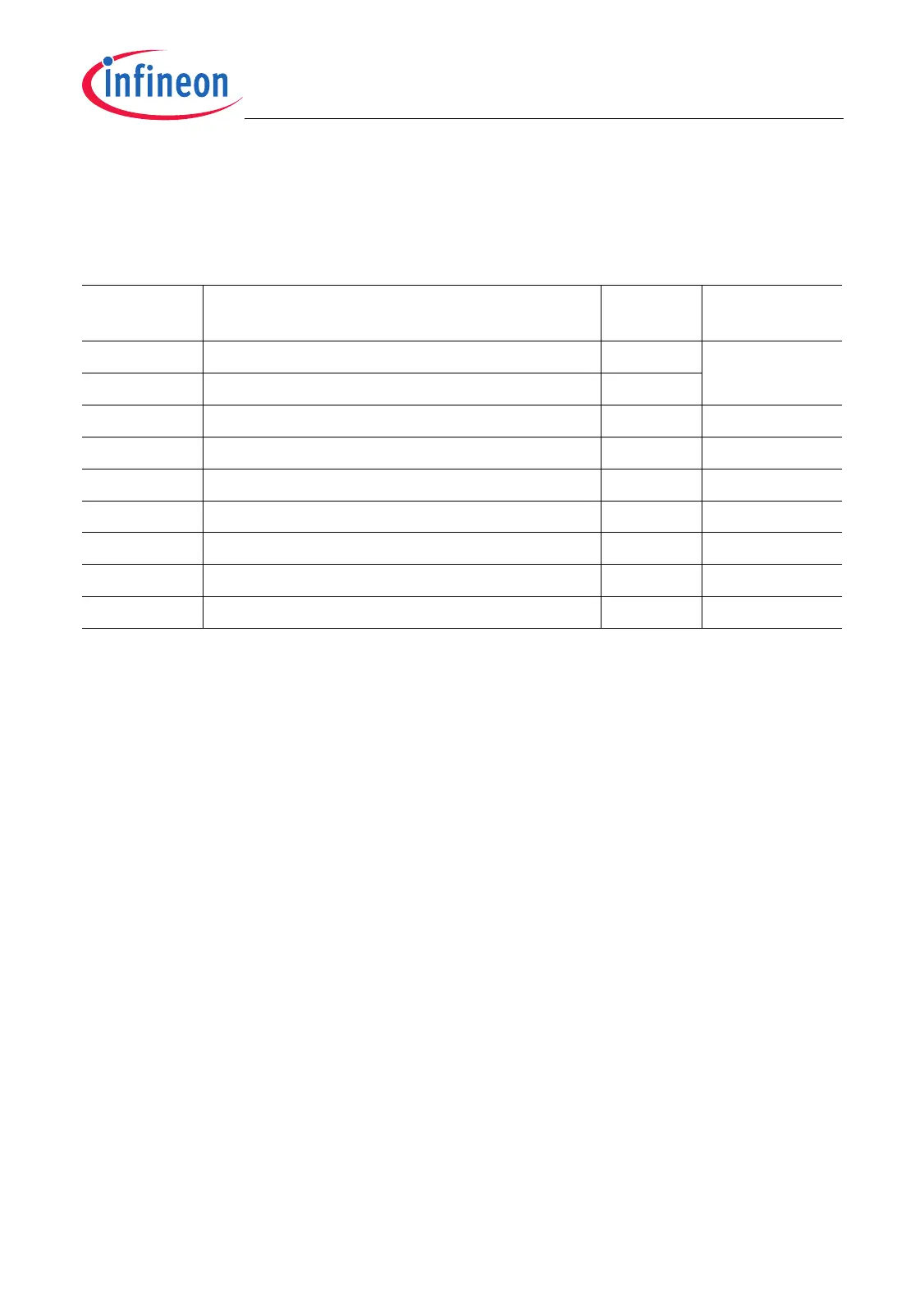

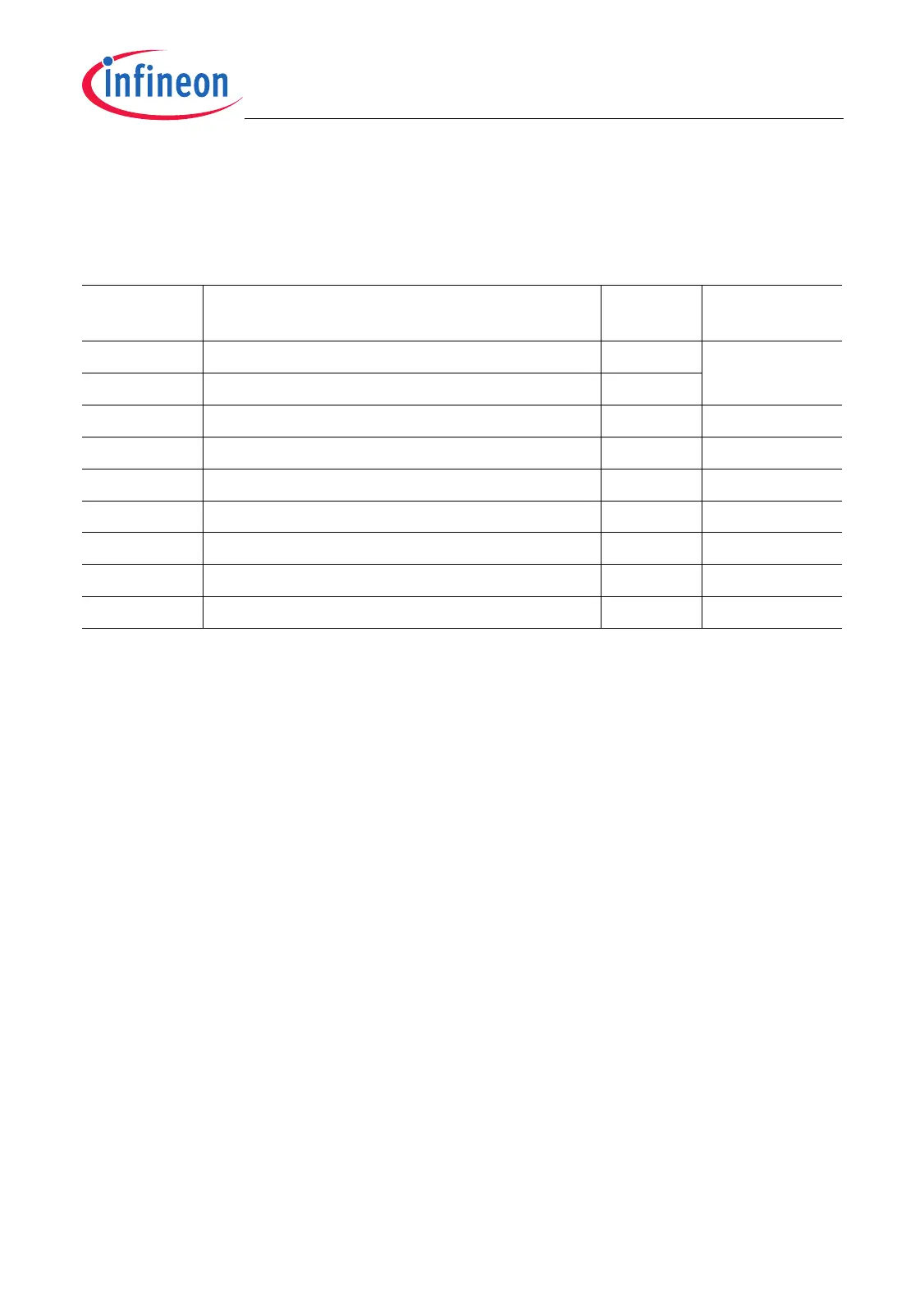

Table 10-12 Port 2 Registers

Register

Short Name

Register Long Name Offset

Address

Description

see

P2_OUT Port 2 Output Register 0000

H

below

1)

1) These registers are listed and noted here in the Port 2 section because they differ from the general port

register description given in Section 10.2.

P2_OMR Port 2 Output Modification Register 0004

H

P2_IOCR0 Port 2 Input/Output Control Register 0 0010

H

Page 10-38

1)

P2_IOCR4 Port 2 Input/Output Control Register 4 0014

H

Page 10-8

P2_IOCR8 Port 2 Input/Output Control Register 8 0018

H

Page 10-8

P2_IOCR12 Port 2 Input/Output Control Register 12 001C

H

Page 10-9

P2_IN Port 2 Input Register 0024

H

Page 10-38

1)

P2_PDR Port 2 Pad Driver Mode Register 0040

H

Page 10-39

1)

P2_ESR Port 2 Emergency Stop Register 0050

H

Page 10-39

1)

Loading...

Loading...