TC1796

Peripheral Units (Vol. 2 of 2)

Micro Link Interface (MLI)

User’s Manual 23-61 V2.0, 2007-07

MLI, V2.0

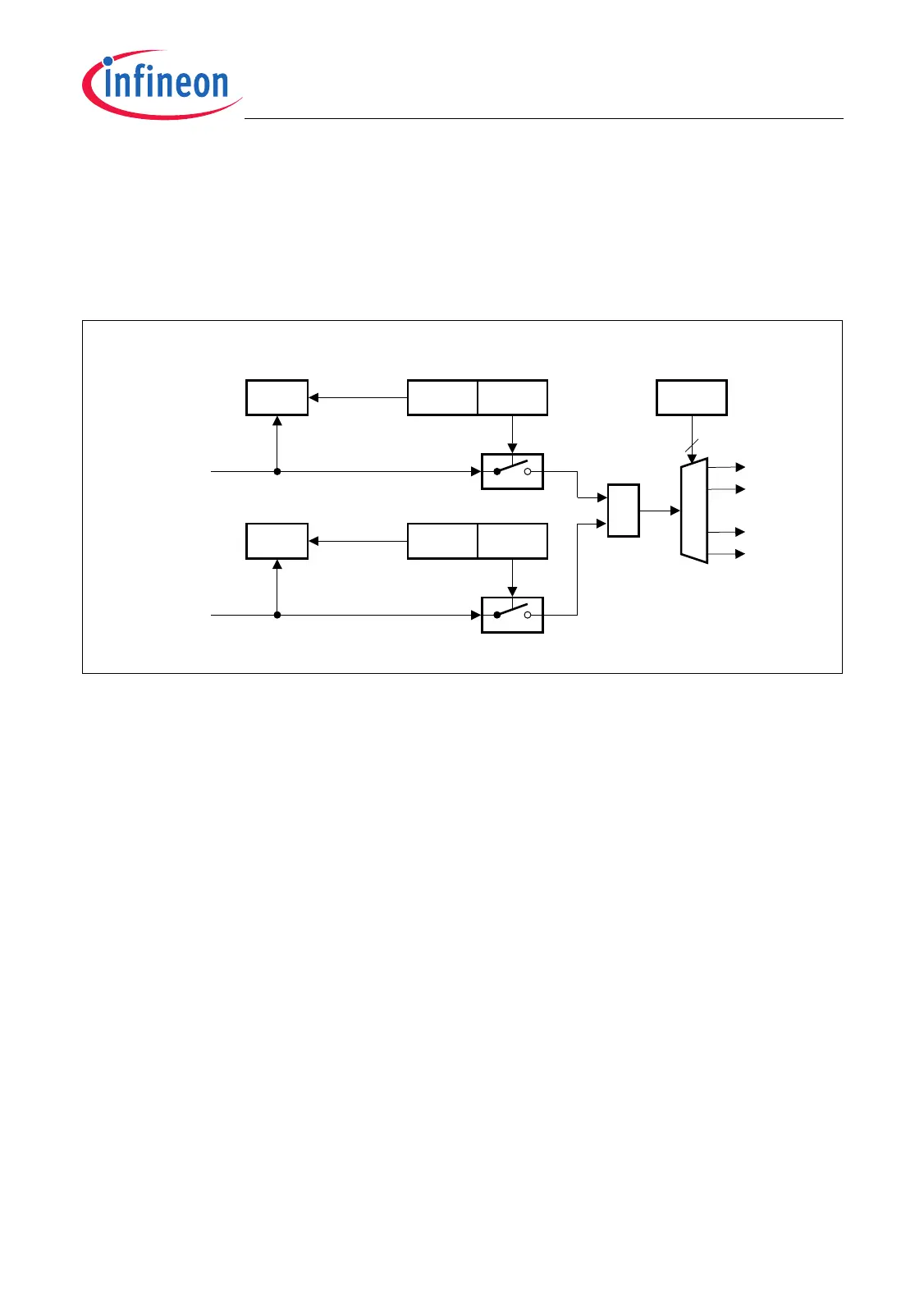

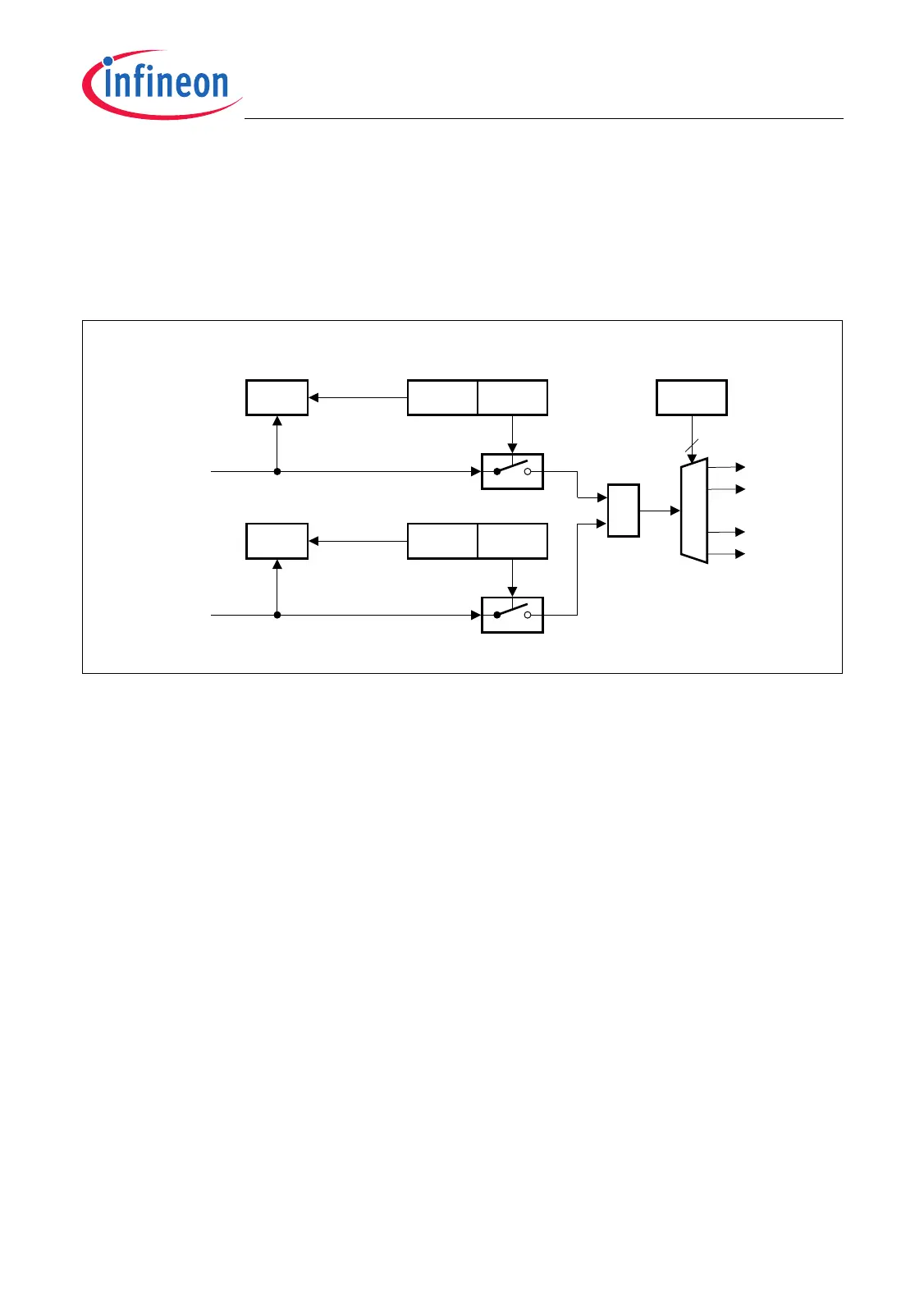

23.2.6.2 Memory Access Protection/Parity Error Event

A memory access protection/parity error event is detected if a non allowed read or write

access has been detected or if a programmable maximum number of receiver parity

errors is reached. Both MLI events have separate status/control bits but are

concatenated to one common error event.

Figure 23-43 Memory Access Protection/Parity Error Event Logic

MCA05900_mod

MPEIE

RIER

MPEIR

Software

Clear

PEIE

RIER

PEIR

Software

Clear

Memory

Protection/

Parity Error

Event

MPEI

RISR

Set

PEI

RISR

Set

Memory

Protection

Error Event

Parity Error

Event

3

To SR0

To SR1

To SR6

To SR7

.

.

.

.

.

.

MPPEIP

RINPR

≥1

Loading...

Loading...