TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual 22-42 V2.0, 2007-07

MultiCAN, V2.0

22.3.9.2 Pending Messages

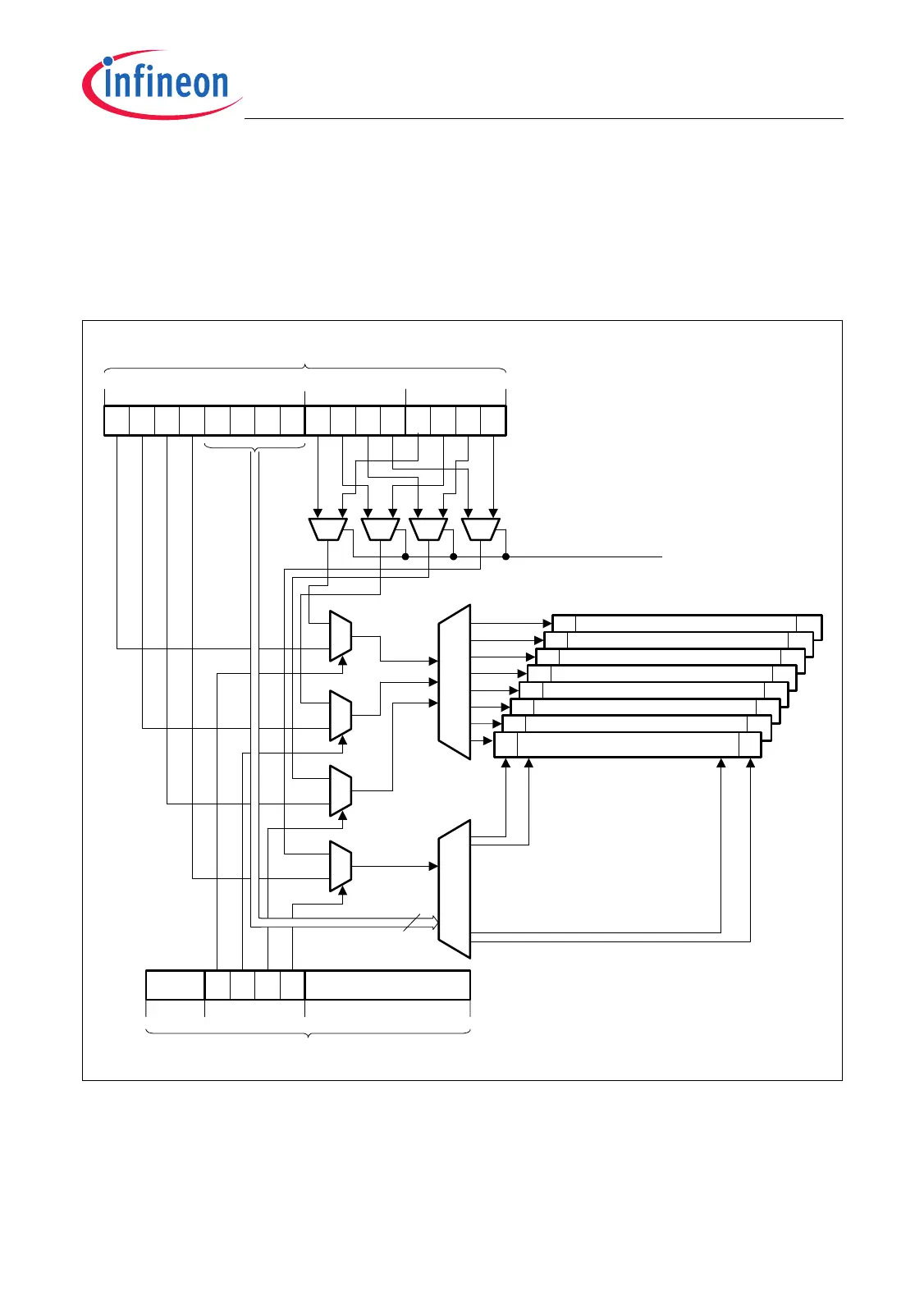

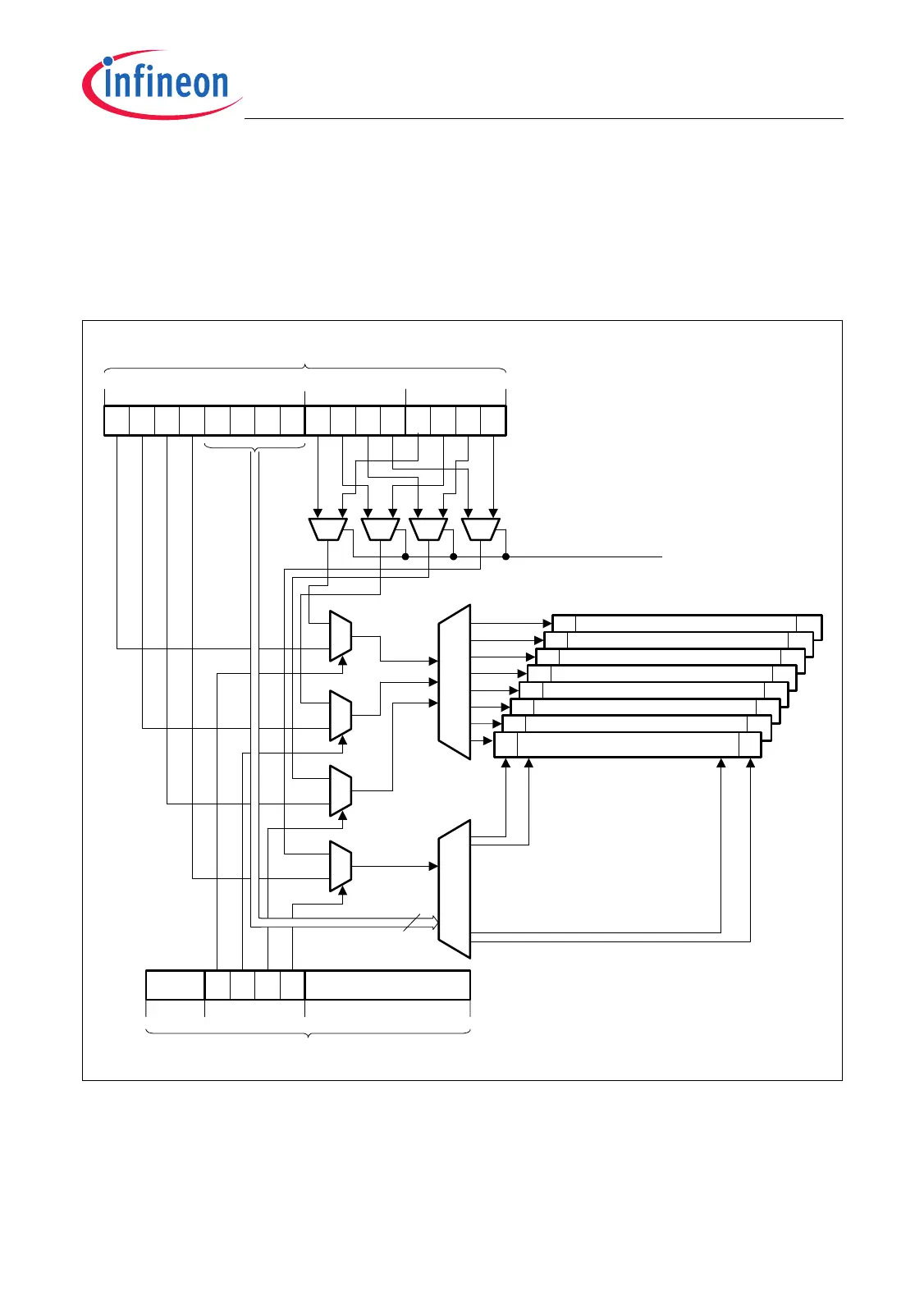

When a message interrupt request is generated, a message pending bit is set in one of

the Message Pending Registers. There are eight Message Pending Registers, MSPNDk

(k = 0-7), with 32 pending bits available each, resulting in 256 pending bits. Figure 22-18

shows the allocation of the message pending bits.

Figure 22-18 Message Pending Bit Allocation

The location of a pending bit is defined by two demultiplexers selecting the number k of

the MSPNDk registers (3-bit demux), and the bit location within the corresponding

MSPNDk register (5-bit demux).

255 224

MCA05844

7 6 5 4 3 2 1 0

MPN

Message Object n Interrupt Pointer Register MOIPRn[15:0]

3 2 1 0

TXINP

3 2 1 0

RXINP

15

D

E

M

U

X

0

7

D

E

M

U

X

0

31

31

0

. . . . . . . . . . . . . . .

. . . . . . . .

4

3 2 1 0

MPSEL

Modul Control Register MCR[31:0]

MSB

Message Pending Registers

0 = transmit event

1 = receive event

223

159

191

127

95

63

192

160

128

96

64

32

MSPND0

MSPND1

MSPND2

MSPND3

MSPND4

MSPND5

MSPND6

MSPND7

2

1

0

7

6

5

4

3:0

31

0

0

0

1

0

1

0

1

01 01 01 01

0

1

Loading...

Loading...