TC1796

Peripheral Units (Vol. 2 of 2)

Fast Analog-to-Digital Converter (FADC)

User’s Manual 26-63 V2.0, 2007-07

FADC, V2.0

26.3.5 Interrupt Control

Each of the four FADC interrupts is controlled by a service request control register.

Note: Additional details on service request nodes and the service request control

registers are described on Page 14-3 of the TC1796 User’s Manual System Units

part (Volume 1).

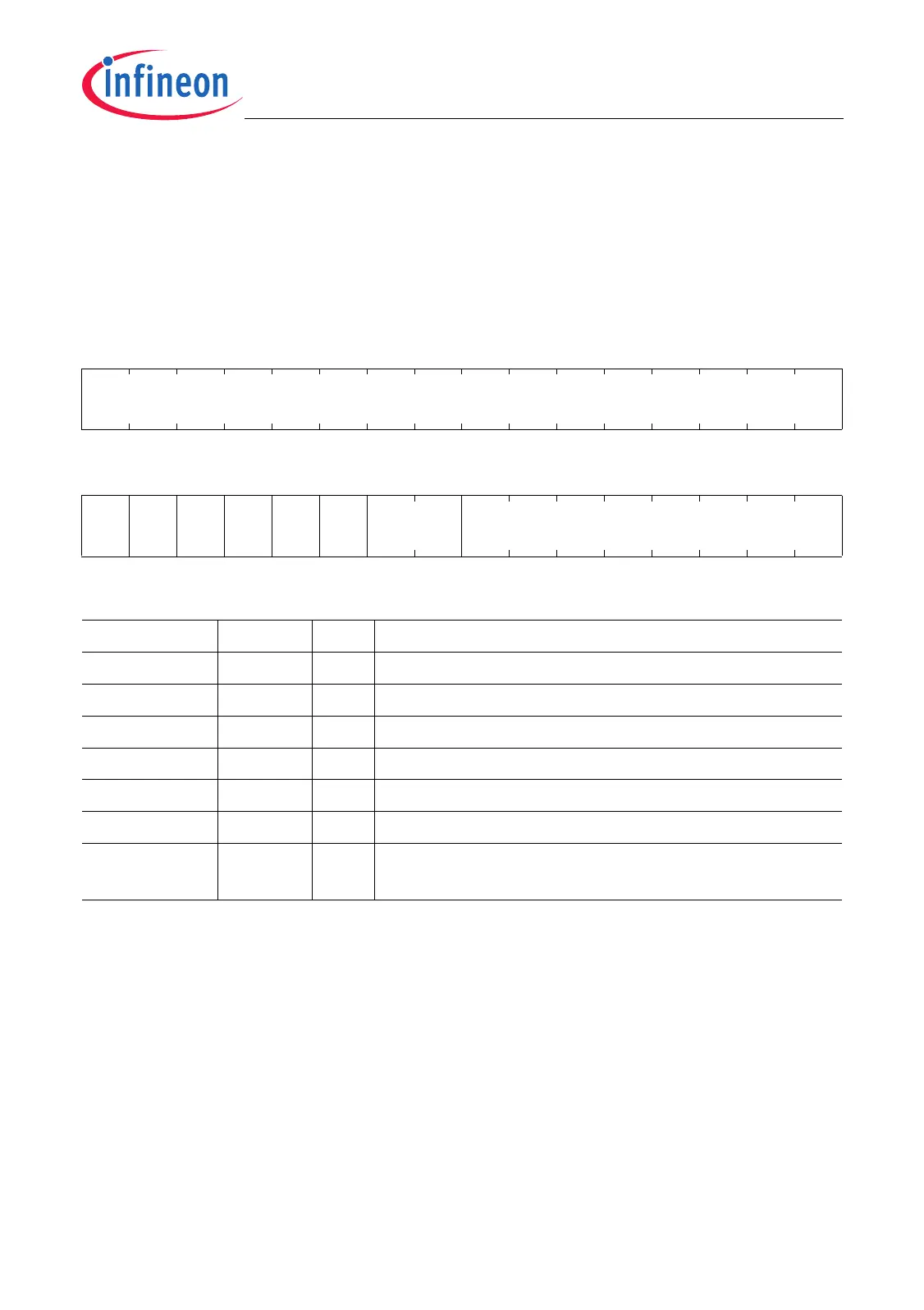

FADC_SRCm (m = 0-3)

FADC Service Request Control Register m

(FC

H

-m*4

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

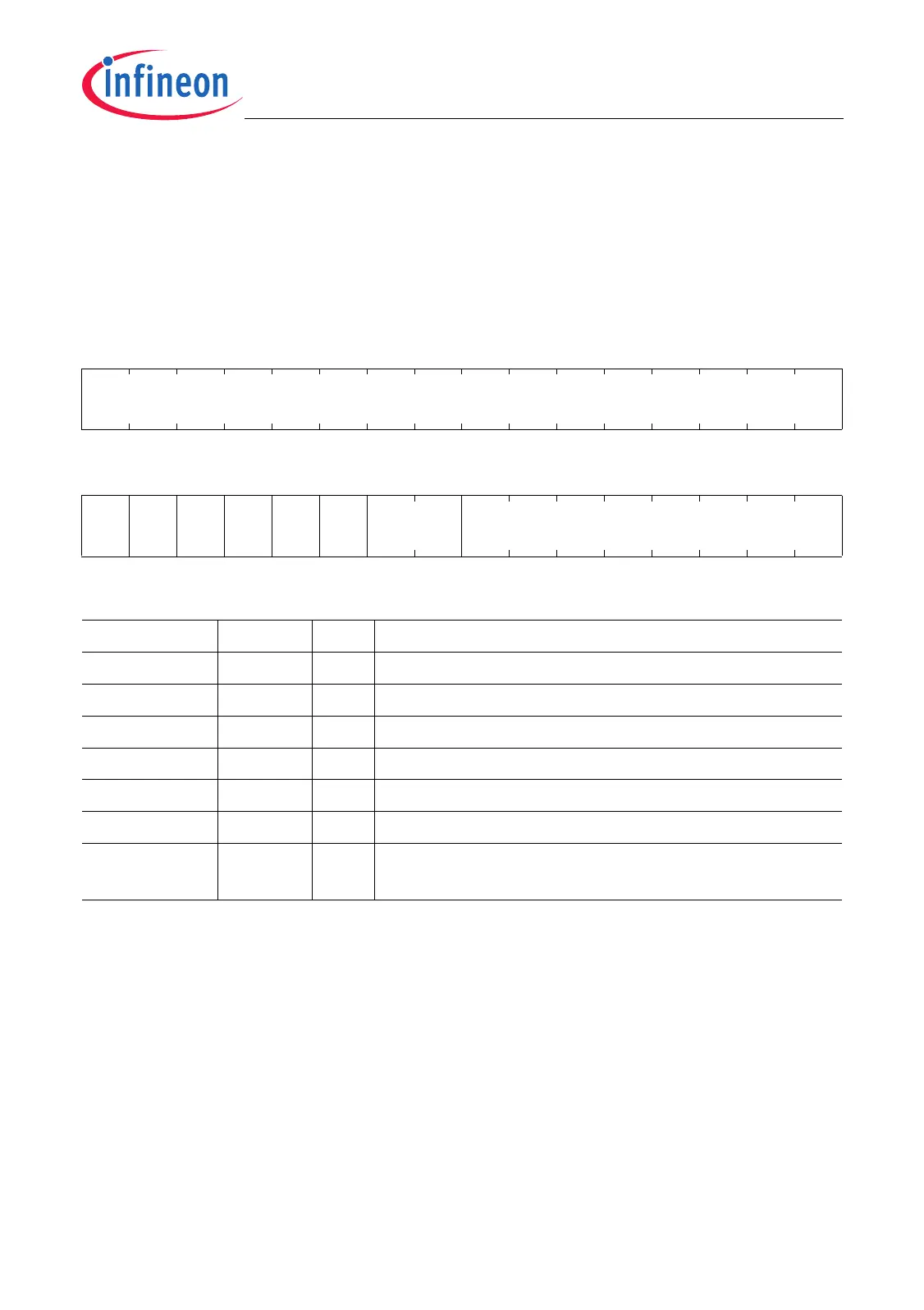

SET

R

CLR

R

SRR SRE 0 TOS 0 SRPN

wwrhrwrrw rrw

Field Bits Type Description

SRPN [7:0] rw Service Request Priority Number

TOS 10 rw Type of Service Control

SRE 12 rw Service Request Enable

SRR 13 rh Service Request Flag

CLRR 14 w Request Clear Bit

SETR 15 w Request Set Bit

0 [9:8], 11,

[31:16]

r Reserved

Read as 0; should be written with 0.

Loading...

Loading...