TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-17 V2.0, 2007-07

CPU, V2.0

2.4.4 Core Debug Registers

In the TC1796, several Core Debug registers are available for debug purposes. These

Core Debug registers are described in detail in the TriCore 1 Architecture Manual

chapter - Core Debug Controller.

Figure 2-9 Core Debug Registers

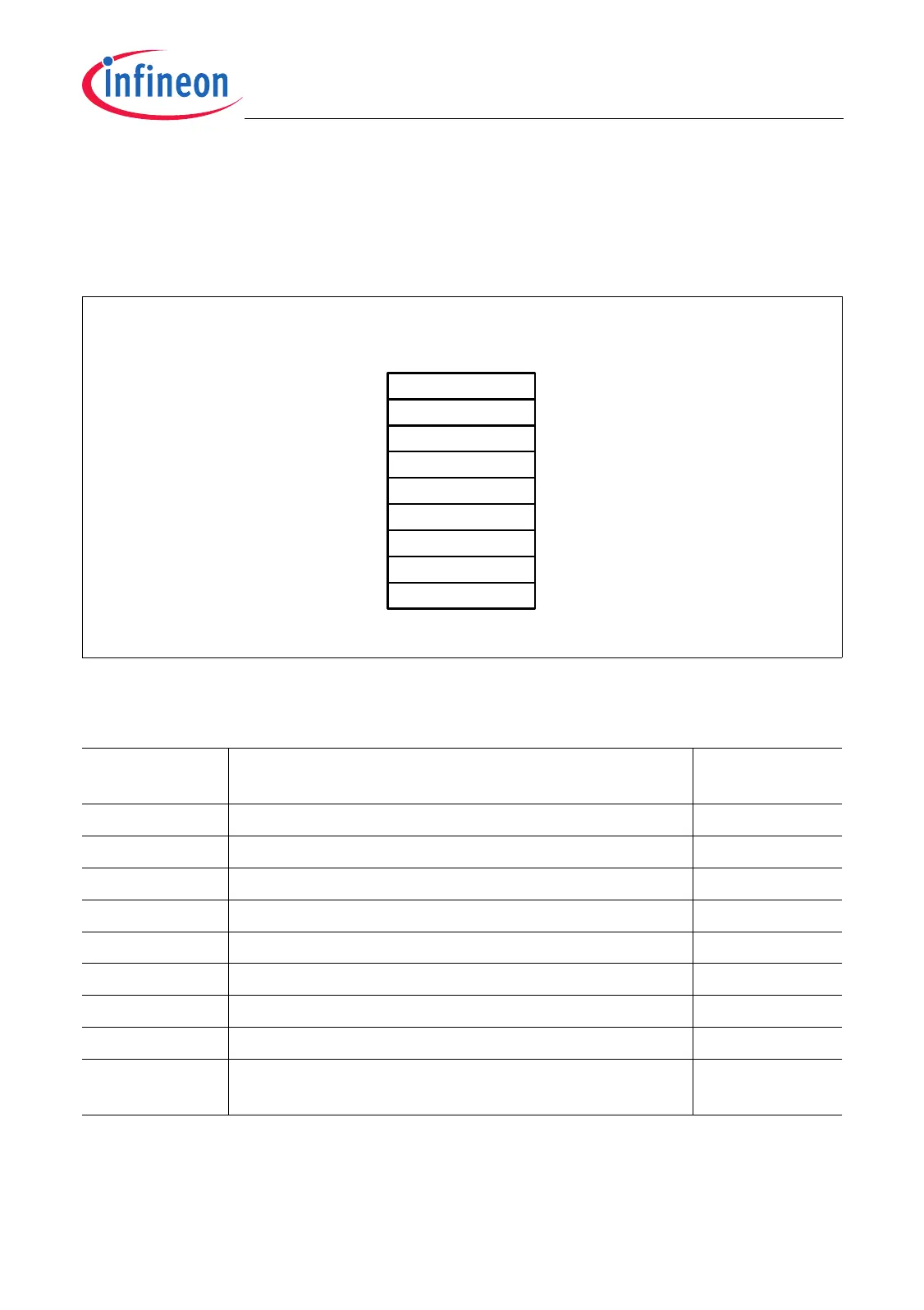

Table 2-5 Core Debug Registers

Register Short

Name

Register Long Name Address

DBGSR Debug Status Register F7E1 FD00

H

EXEVT External Break Input Event Specifier Register F7E1 FD08

H

CREVT Core SFR Access Break Event Specifier Register F7E1 FD0C

H

SWEVT Software Break Event Specifier Register F7E1 FD10

H

TR0EVT Trigger Event 0 Specifier Register F7E1 FD20

H

TR1EVT Trigger Event 1 Specifier Register F7E1 FD24

H

DMS Debug Monitor Start Address Register F7E1 FD40

H

DCX Debug Context Save Area Pointer F7E1 FD44

H

CPU_SBSCR0 CPU Software Breakpoint Service Request Control

Register 0

see Table 2-3

1)

1) Located in the CPU slave (CPS) interface register area.

MCA05593

DBGSR

Core Debug

Registers

EXEVT

CREVT

SWEVT

TR0EVT

TR1EVT

DMS

DCX

CPU_SBSRC0

Loading...

Loading...