TC1796

System Units (Vol. 1 of 2)

Clock System and Control

User’s Manual 3-32 V2.0, 2007-07

Clock, V2.0

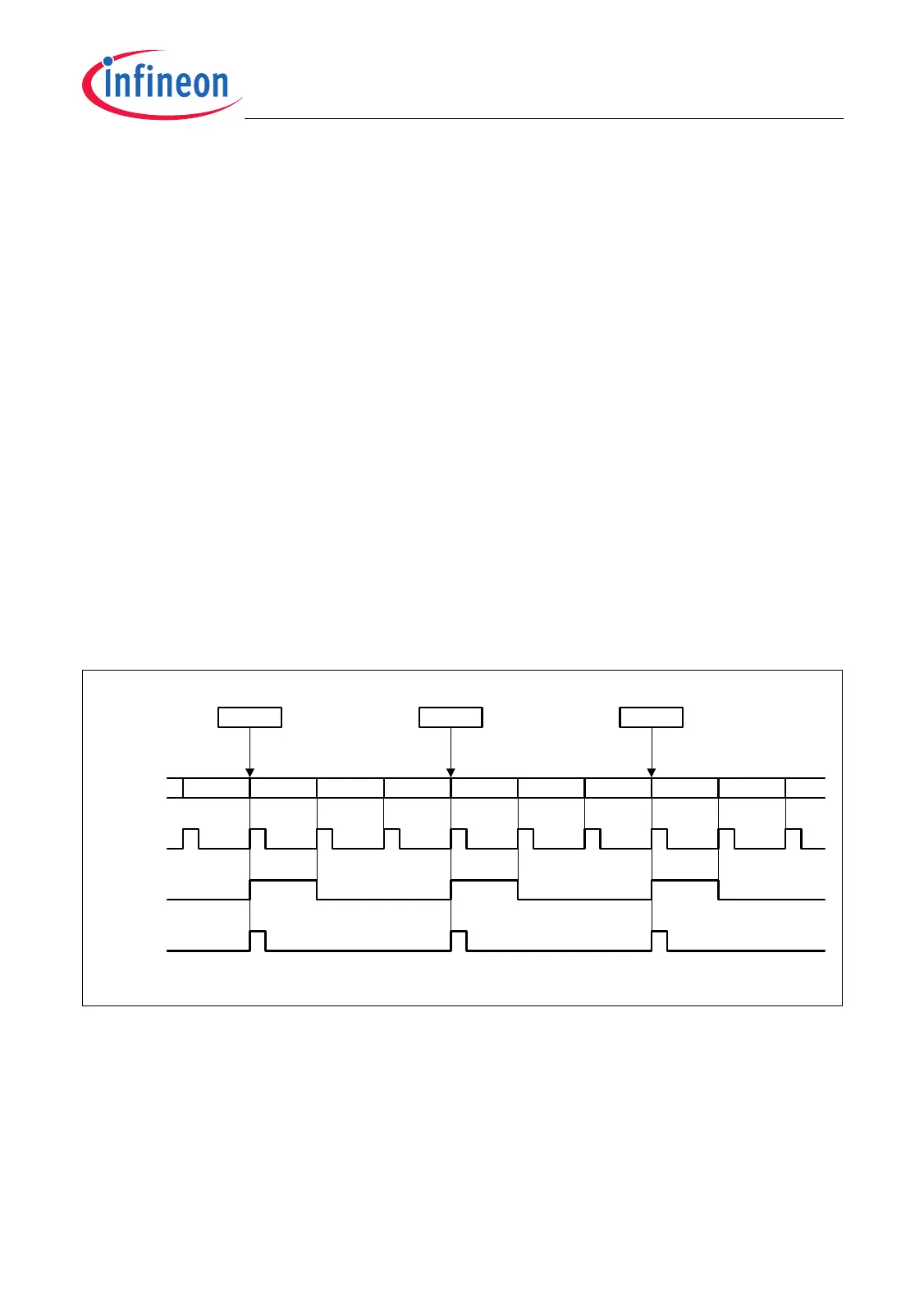

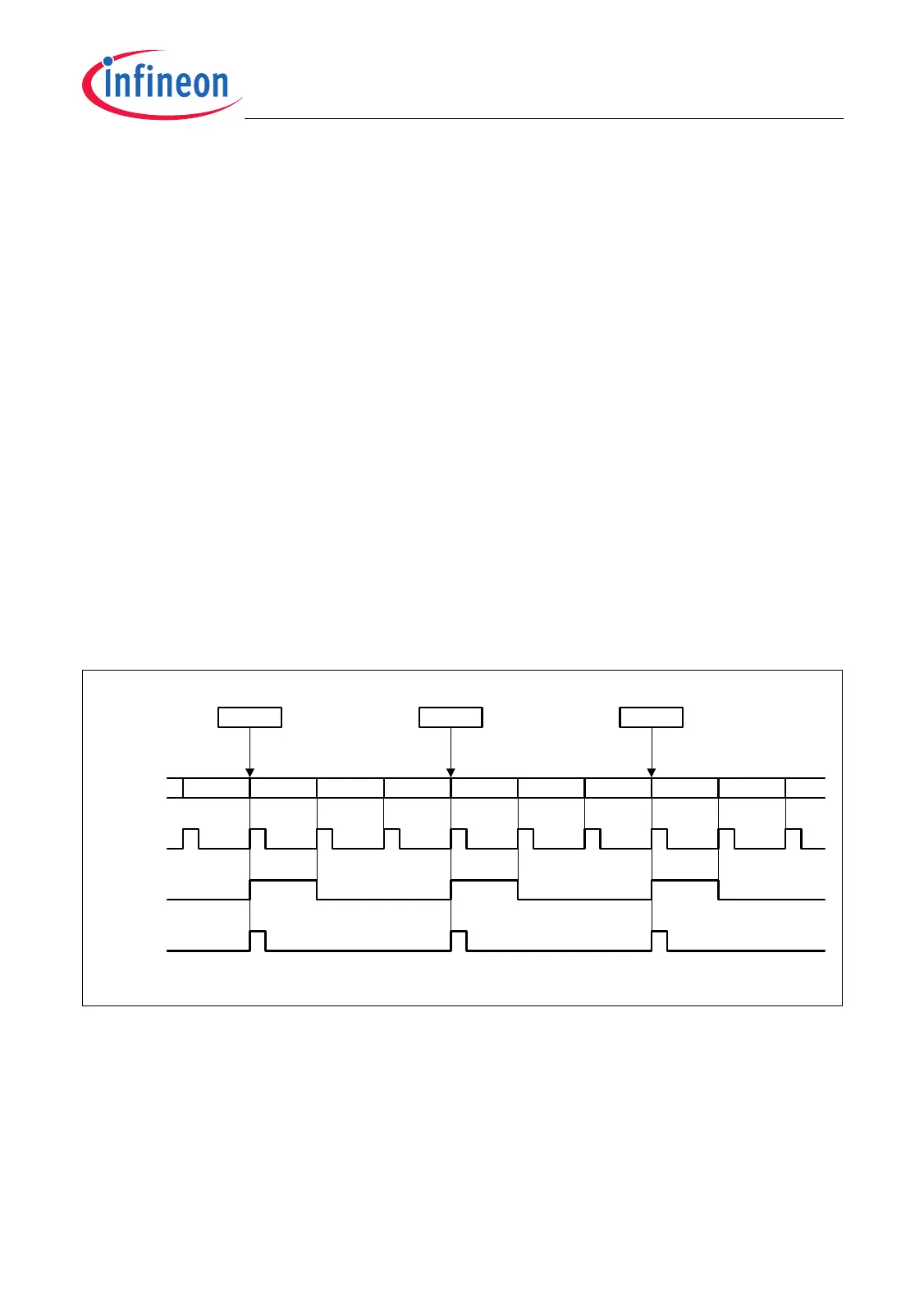

3.3.3.2 Fractional Divider Operating Modes

The fractional divider has two operating modes:

• Normal divider mode

• Fractional divider mode

Normal Divider Mode

In normal divider mode (FDR.DM = 01

B

), the fractional divider behaves as a reload

counter (addition of +1) that generates an output clock pulse at f

OUT

on the transition from

3FF

H

to 000

H

. FDR.RESULT represents the counter value and FDR.STEP determines

the reload value.

The output frequencies in normal divider mode are defined according to the following

formulas:

(3.5)

In order to get

f

OUT

= f

IN

STEP must be programmed with 3FF

H

. Figure 3-7 shows the

operation of the normal divider mode with a reload value of FDR.STEP = 3FD

H

. The

clock signal f

OUT

is the AND combination of the f

OUT

Enable signal with f

IN

.

Figure 3-7 Normal Mode Timing

f

OUT

f

IN

1

n

---×=

, with n = 1024 - STEP

MCT05605

RESULT 3FF

f

IN

3FE3FD 3FF 3FD3FD 3FE 3FF

3FD

3FE

STEP

Reload

3FD

Reload

3FD

Reload

f

OUT

Enable

f

OUT

Loading...

Loading...