TC1796

System Units (Vol. 1 of 2)

System Control Unit

User’s Manual 5-64 V2.0, 2007-07

SCU, V2.0

5.13 Miscellaneous SCU Registers

This section includes descriptions of the following registers:

• SCU Control Register SCU_CON

• SCU Status Register SCU_STAT

• SCU Module Identification Register SCU_ID

• Manufacturer Identification Register MANID

• Chip Identification Register CHIPID

• Redesign Tracing Identification Register RTID

5.13.1 SCU Control Register

SCU_CON

SCU Control Register (F0000050

H

) Reset Value: FF00 0002

H

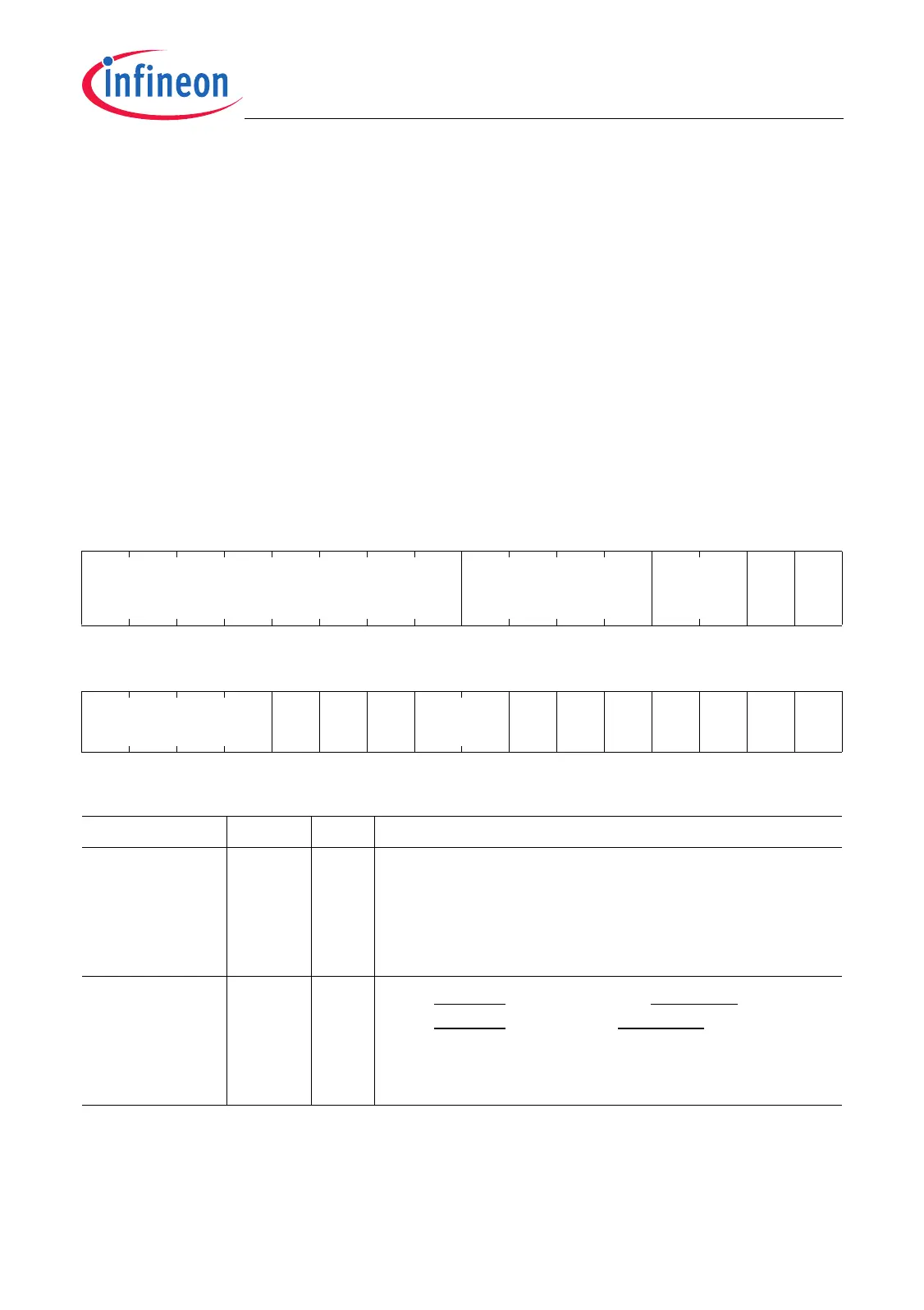

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ONE ZERO GIN1S

SSC

0

PDR

SLS

PDR

rw rw rw rw rw

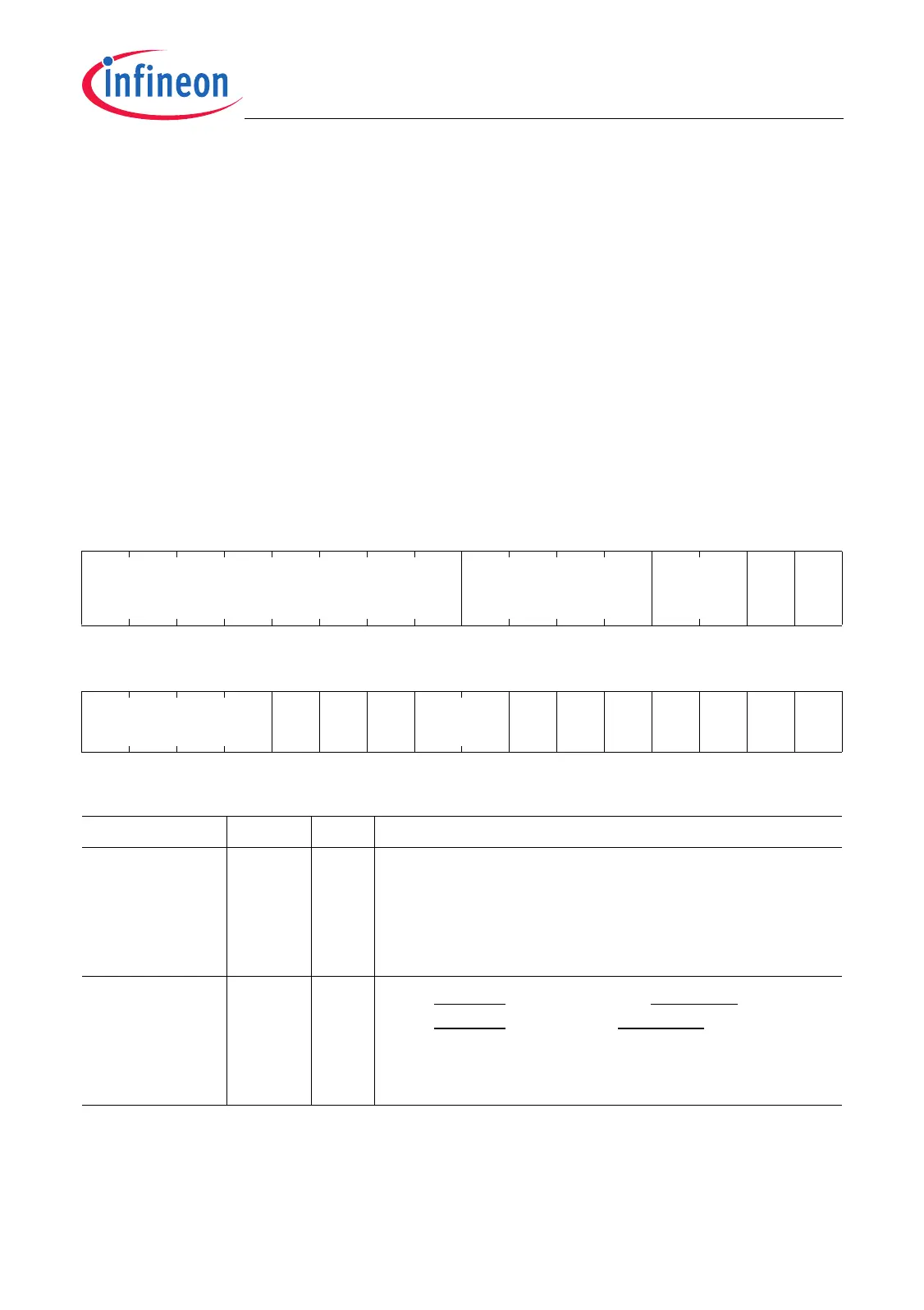

1514131211109876543210

0

RPA

RAV

LD

EN

DTS

ON

0

AN7

TM

NMI

EN

EPU

D

CS

GEN

CS

OEN

CS

EEN

FIEN

r rwrwrw r rwrwsrwrwrwrwrw

Field Bits Type Description

FIEN 0rwFPU Inexact Interrupt Enable

0

B

Inexact error condition (setting FX flag) after a

FPU calculation will not generate an interrupt.

1

B

Inexact error condition (setting FX flag) after a

FPU calculation will generate an interrupt.

CSEEN 1rwCSEMU Enable

0

B

CSEMU will not activate CSCOMB

1

B

CSEMU will activate CSCOMB

(default after reset)

See also Figure 13-10 on Page 13-29.

Loading...

Loading...