TC1796

Peripheral Units (Vol. 2 of 2)

Fast Analog-to-Digital Converter (FADC)

User’s Manual 26-30 V2.0, 2007-07

FADC, V2.0

26.2.2 Global Registers

The Conversion Request Status Register CRSR contains the flags for monitoring the

state of pending conversions and the interrupt request flags.

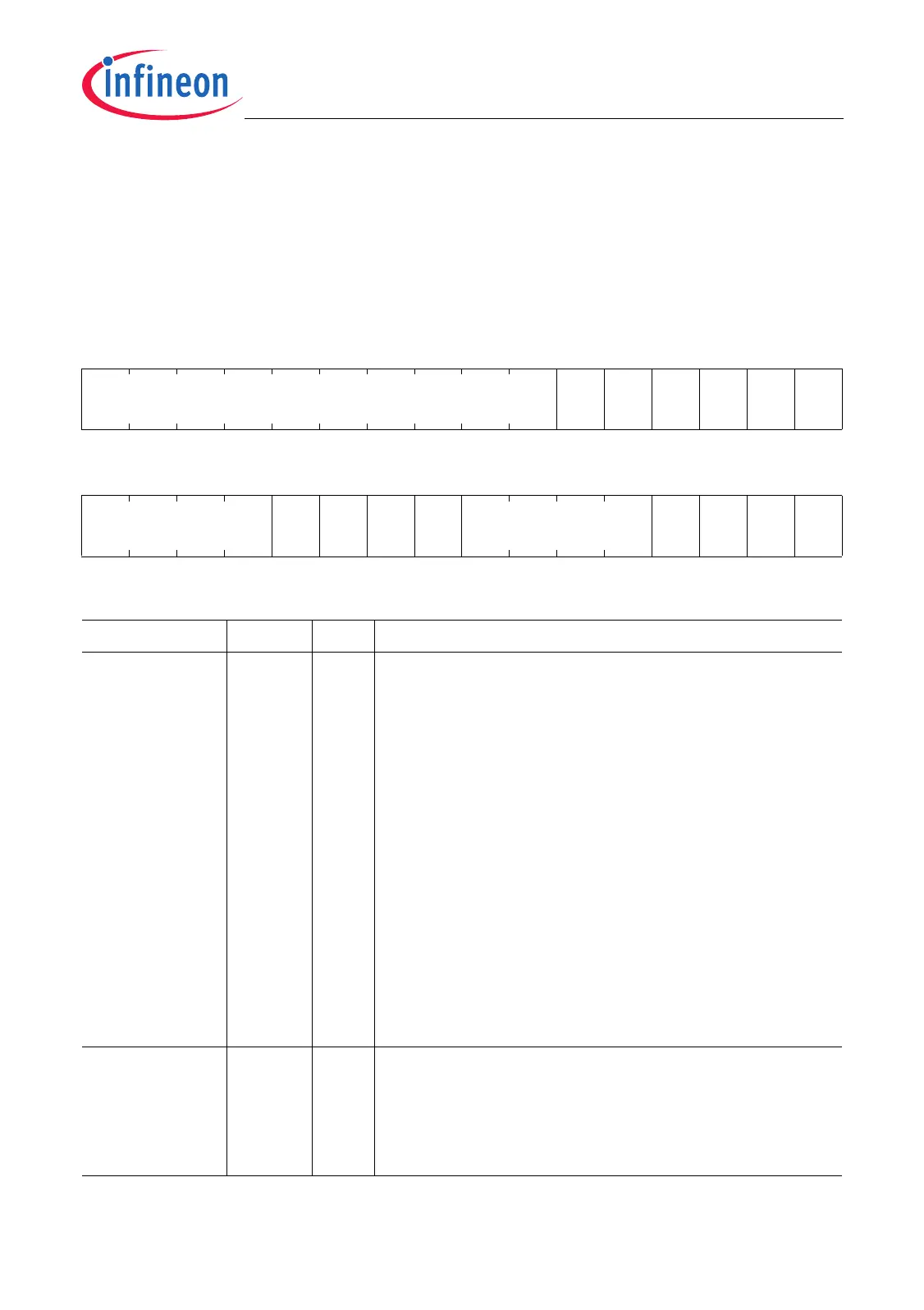

CRSR

Conversion Request Status Register (10

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

IRQ

F1

IRQ

F0

IRQ

3

IRQ

2

IRQ

1

IRQ

0

r rhrhrhrhrhrh

1514131211109876543210

0

BSY

3

BSY

2

BSY

1

BSY

0

0

CRF

3

CRF

2

CRF

1

CRF

0

r rhrhrhrh r rhrhrhrh

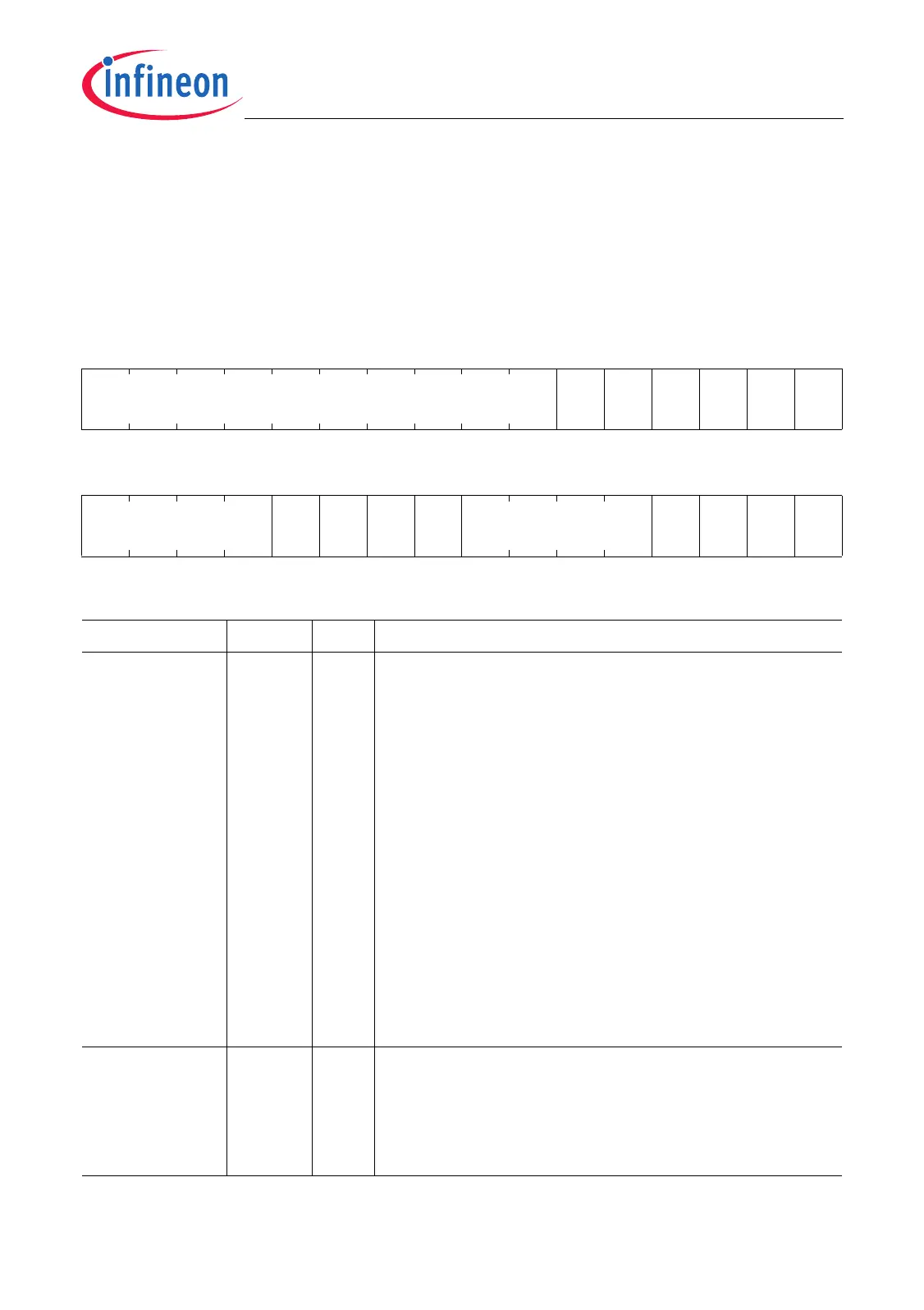

Field Bits Type Description

CRFx

(x = 0-3)

xrhConversion Request Flag

This bit monitors whether a conversion request is

pending for channel x. CRFx is set by hardware

when a trigger event is detected while the gating

condition delivers 1. CRFx is automatically cleared

by hardware when a conversion of the channel x is

started.

0

B

A conversion of channel x has not been

requested.

1

B

A conversion of channel x has been

requested.

Bits CRFx can be set/cleared by software via bits

FMR.RCRFx and FMR.SCRFx (see Page 26-32).

If a set and a clear condition for CRFx occur

simultaneously (generated by hardware and/or

software), the clear condition always wins.

BSYx

(x = 0-3)

8 + x rh Busy Flag

This bit indicates if a conversion is currently running

for channel x.

0

B

A conversion is not running.

1

B

A conversion is running.

Loading...

Loading...