TC1796

Peripheral Units (Vol. 2 of 2)

Micro Second Channel (MSC)

User’s Manual 21-20 V2.0, 2007-07

MSC, V2.0

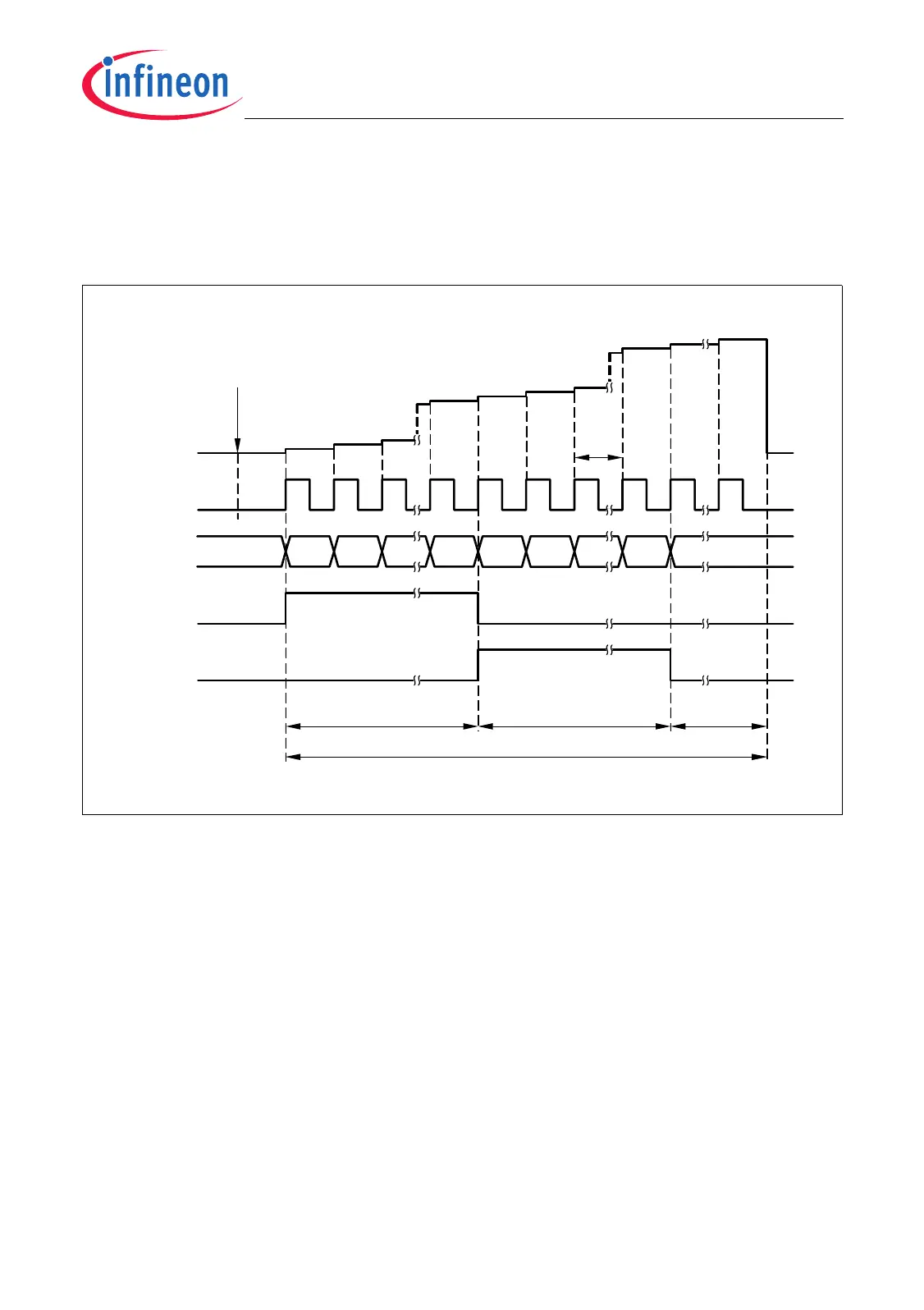

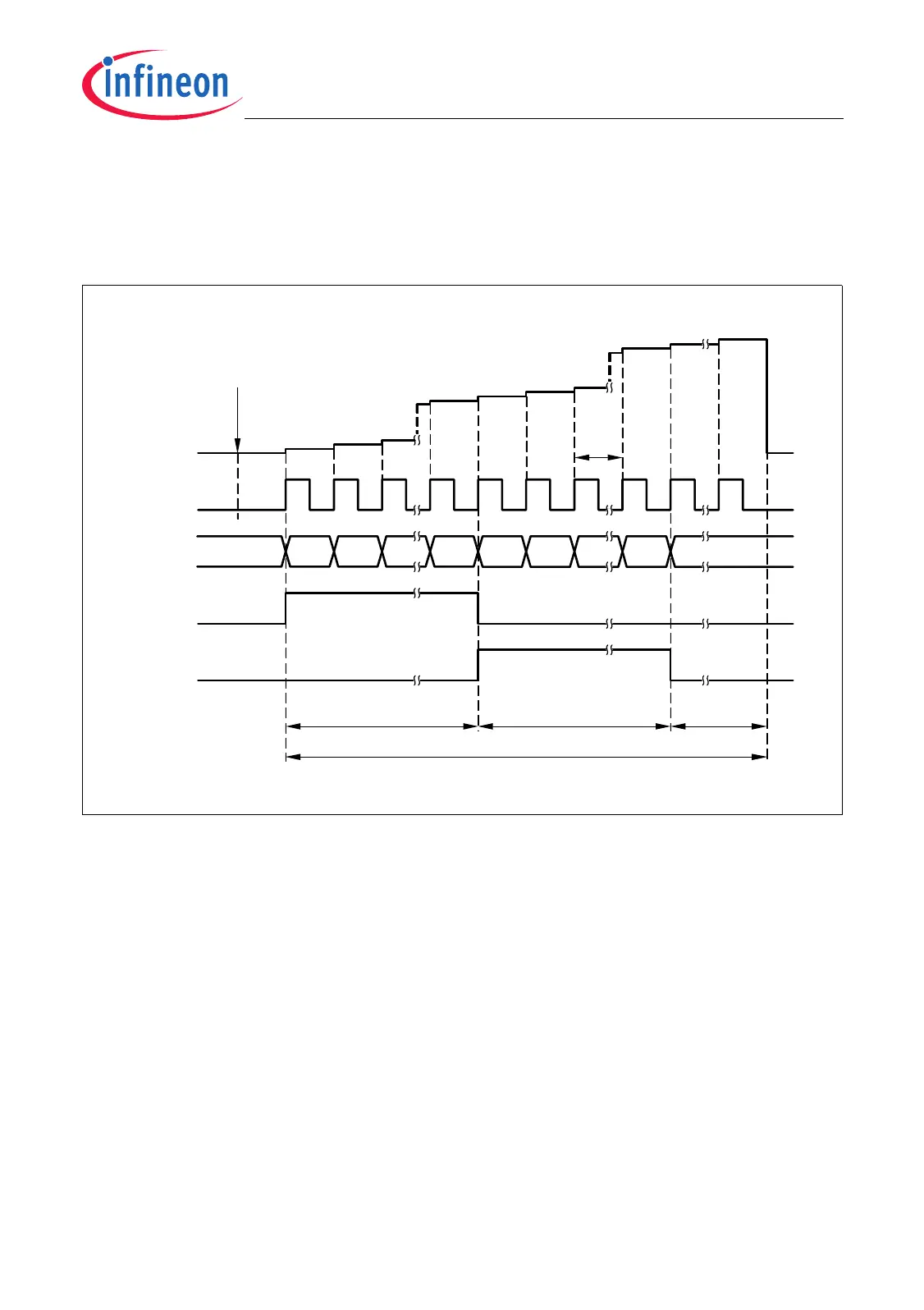

When the selection bit for the SRL active frame is disabled (ENSELL = 0, see

Figure 21-13), the loading of the shift register SRL/SRH (and reset of the downstream

counter) occurs one FCL clock cycle before the first data bit SRL.0 is output. ENL is set

to high level with the beginning of the first data bit SRL.0.

Figure 21-13 Shift Clock Counting: Data Frame with ENSELL = 0 and ENSELH = 0

21.1.2.5 Baud Rate

The baud rate of the downstream channel’s serial transmission is defined by the

frequency of the serial clock FCL, and is always f

MSC

/2. The f

MSC

generation is device

specific and depends on the implementation of the MSC module. The TC1796 specific

clock generation is described on Page 21-65.

21.1.2.6 Abort of Frames

Only a reset condition of the device can abort a current transmission. The MSC module

does not start a new frame transmission when the downstream channel becomes

disabled, the suspend mode is requested, or the sleep mode is entered. If one of these

three conditions becomes active during a running frame transmission, the frame

transmission is completely finished before the requested abort state is entered. Note that

in this case no time frame finished interrupt is generated any more.

MCT05807

Passive

Phase

t

FCL

Downstream Frame

SRL Active Phase SRH Active Phase

1

0

2

m+1

SRL.0 SRL.m

m

SRH.0

m+2

m+3

DC

max

SRL/SRH

Loading

SRL.1

3

SRH.nSRH.1

m+4

ENH

ENL

FCL

State of

DSS.DC

SO

Loading...

Loading...