TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-47 V2.0, 2007-07

CPU, V2.0

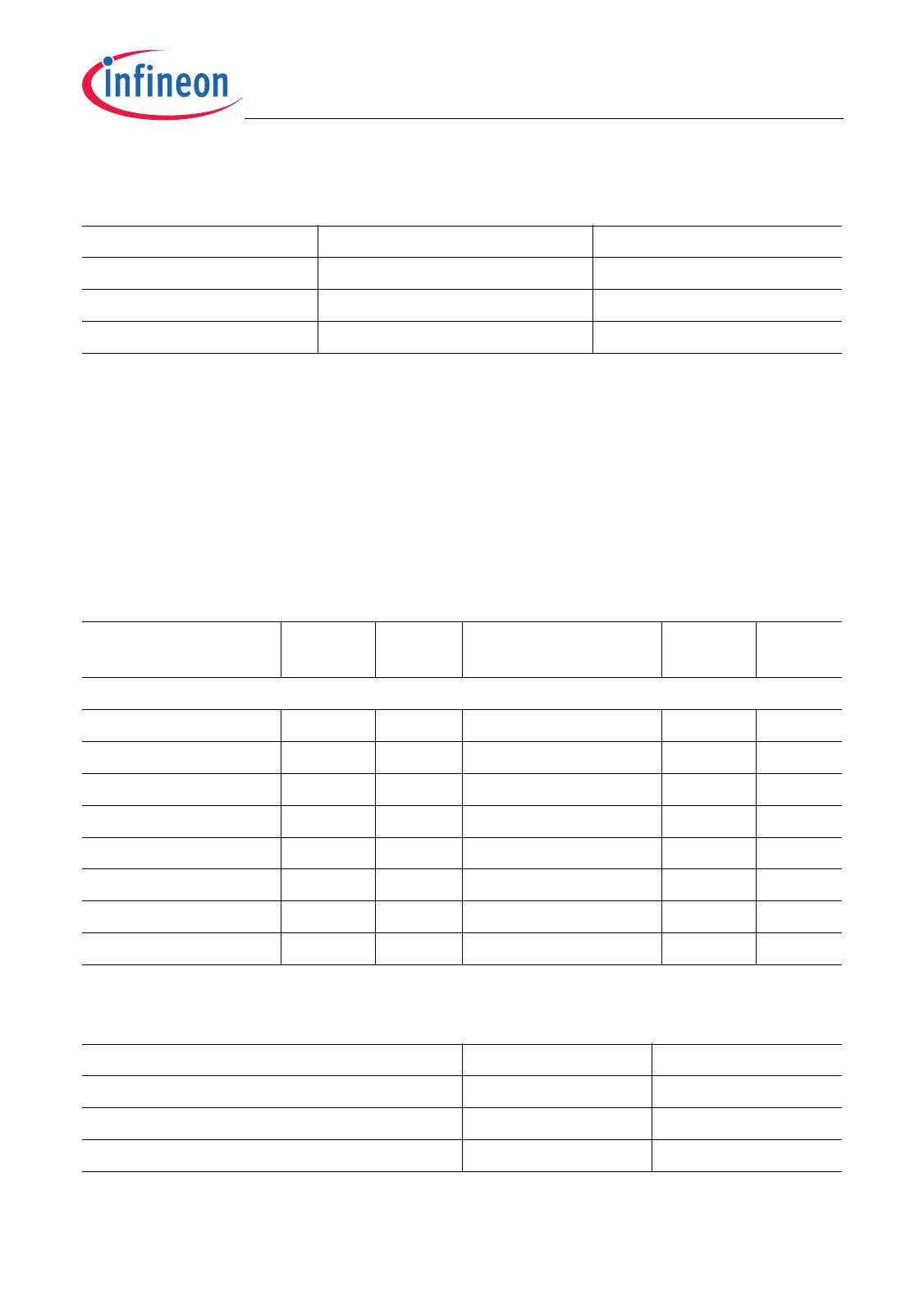

For MADD.Q, MADDS.Q, MSUB.Q, MSUBS.Q Instructions:

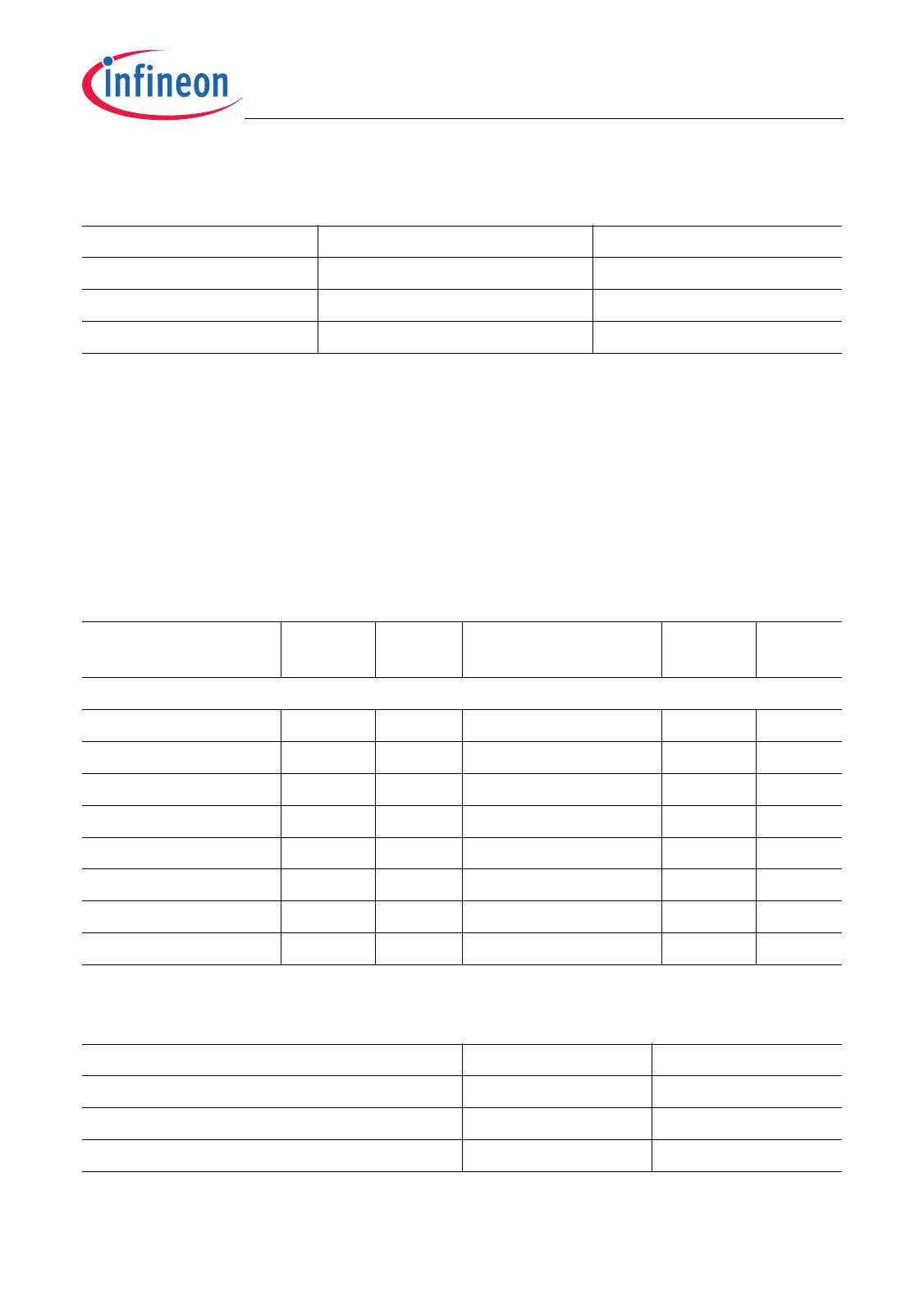

2.7.1.4 Control Flow Instruction Timing

Note all Integer Pipeline Control flow instructions are conditional.

• Each instruction is single issued.

• All target locations yield a full instruction in one access

(i.e. not 16-bits of a 32-bit instruction).

• All code fetches take a single cycle.

• Timing is best case; no cache misses for context operations, no pending stores.

For All Control Flow Instructions:

Result Latency Repeat Rate

16 × 16 2 1

16 × 32 2 1

32 × 32 3 2

Table 2-13 Integer Pipeline Control Flow Instruction Timing

Instruction Flow

Latency

Repeat

Rate

Instruction Flow

Latency

Repeat

Rate

Branch Instructions

JEQ 1/2/3 1/2/3 JLTZ 1/2/3 1/2/3

JGE 1/2/3 1/2/3 JNE 1/2/3 1/2/3

JGE.U 1/2/3 1/2/3 JNED 1/2/3 1/2/3

JGEZ 1/2/3 1/2/3 JNEI 1/2/3 1/2/3

JGTZ 1/2/3 1/2/3 JNZ 1/2/3 1/2/3

JLEZ 1/2/3 1/2/3 JNZ.T 1/2/3 1/2/3

JLT 1/2/3 1/2/3 JZ 1/2/3 1/2/3

JLT.U 1/2/3 1/2/3 JZ.T 1/2/3 1/2/3

Flow Latency Repeat Rate

Correctly predicted, not taken 1 1

Correctly predicted, taken 2 2

Wrongly predicted 3 3

Loading...

Loading...