TC1796

System Units (Vol. 1 of 2)

General Purpose I/O Ports and Peripheral I/O Lines

User’s Manual 10-17 V2.0, 2007-07

Ports, V2.0

Note: Only Port 3 and 4 are 16-bit wide ports used by the GPTA modules. The Pn_ESR

registers of the other ports have a reduced number of bits (see Pn_ESR register

descriptions in the corresponding port sections).

10.2.6 Port Input Register

The logic level of a GPIO pin can be read via the read-only port input register Pn_IN.

When a read of Pn_IN occurs, the values at the GPIO pins are latched in Pn_IN

independently whether the GPIO pin is selected as input or output.

Note: Only Port 0, 1, 3, and 4 are 16-bit wide ports. The Pn_IN registers of the other

ports have a reduced number of Px bits (see Pn_IN register descriptions in the

corresponding port sections).

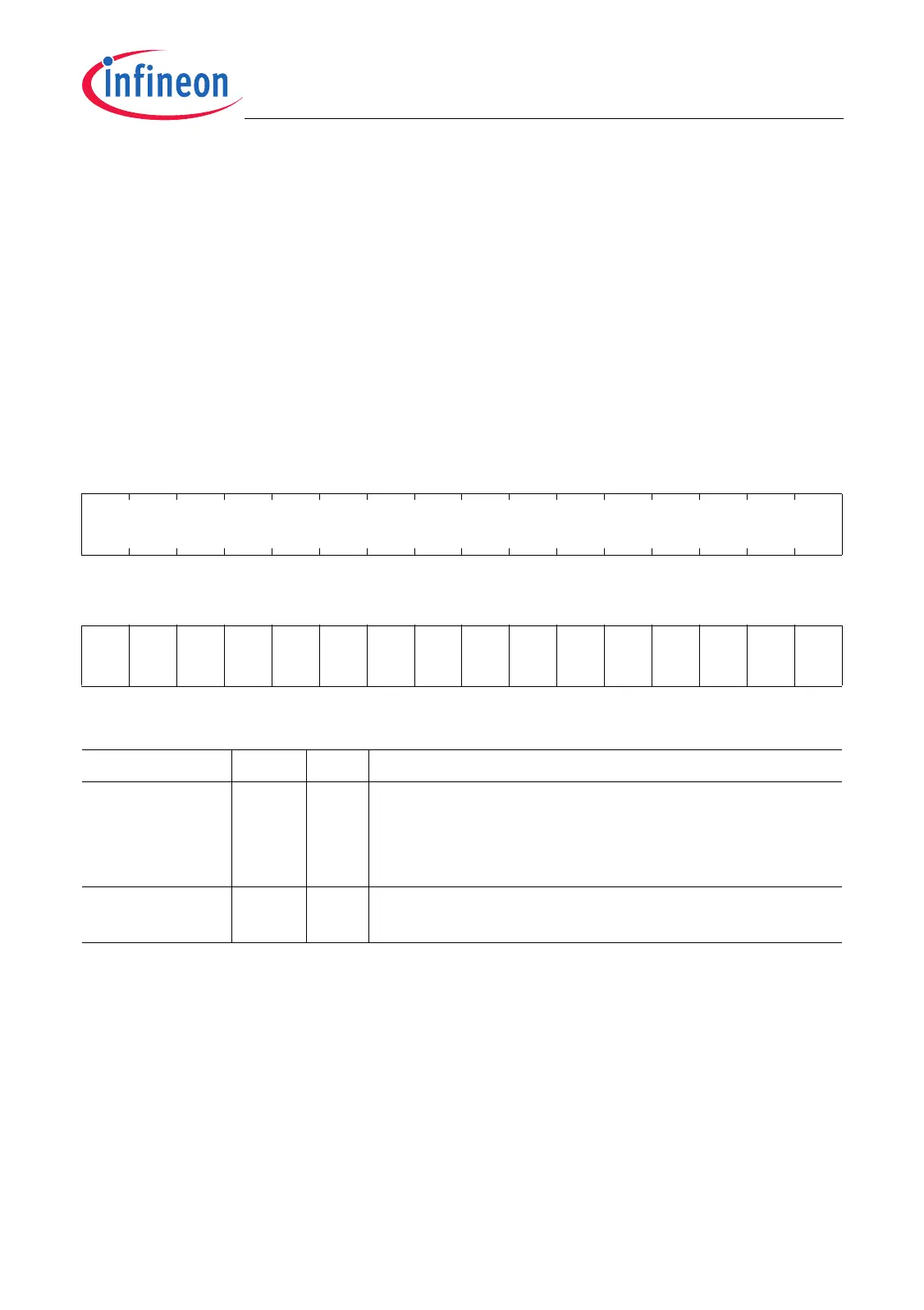

Pn_IN

Port n Input Register (24

H

) Reset Value: 0000 XXXX

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

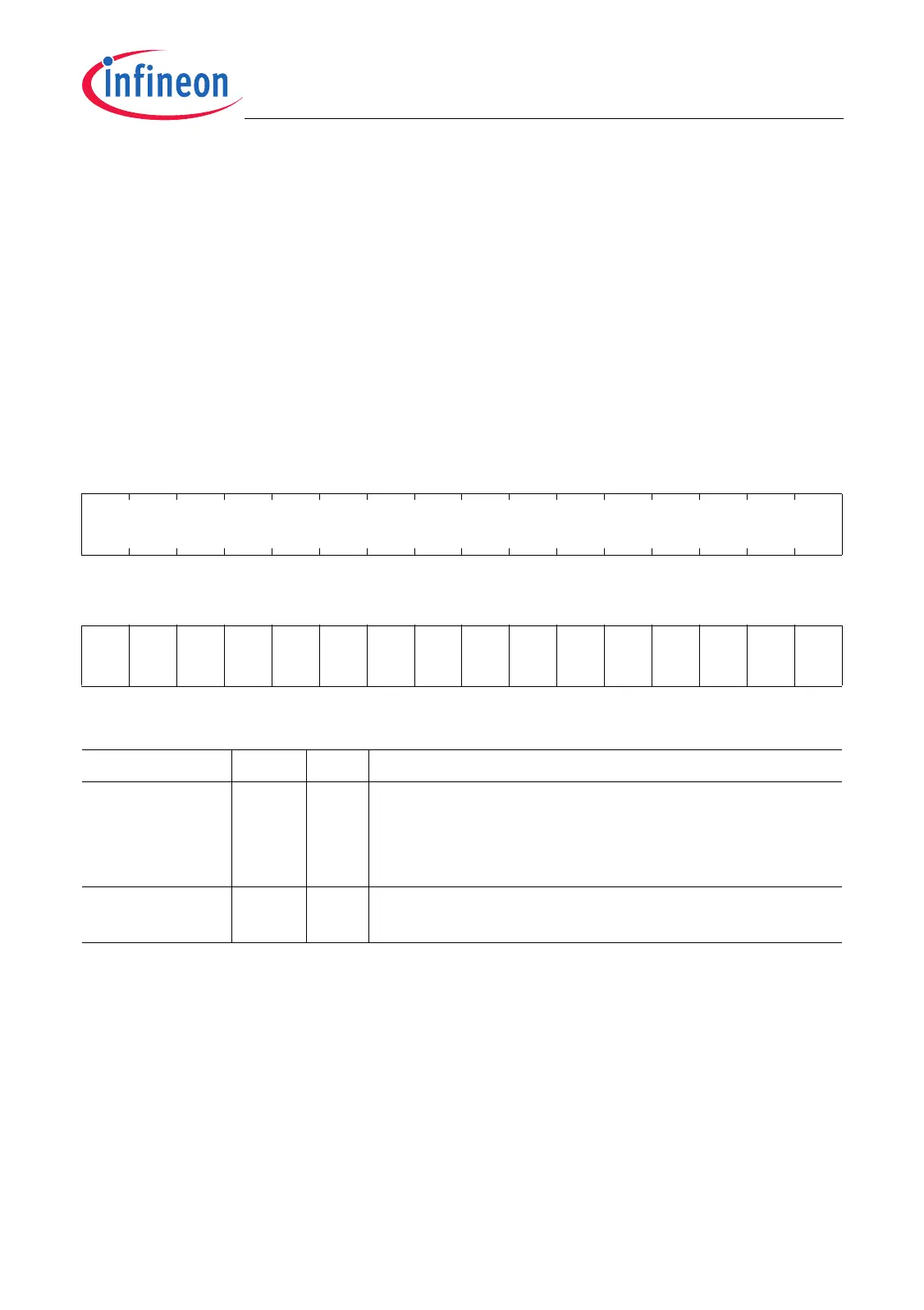

1514131211109876543210

P15 P14 P13 P12 P11 P10 P9 P8 P7 P6 P5 P4 P3 P2 P1 P0

rh rh rh rh rh rh rh rh rh rh rh rh rh rh rh rh

Field Bits Type Description

Px

(x = 0-15)

xrhPort n Input Bit x

This bit indicates the level at the input pinPn.x.

0

B

The input level of Pn.x is 0.

1

B

The input level of Pn.x is 1.

0 [31:16] r Reserved

Read as 0.

Loading...

Loading...