TC1796

System Units (Vol. 1 of 2)

Peripheral Control Processor (PCP)

User’s Manual 11-56 V2.0, 2007-07

PCP, V2.0

11.10.3 PCP Control and Status Register, PCP_CS

This register can be Endinit-protected via bit EIE.

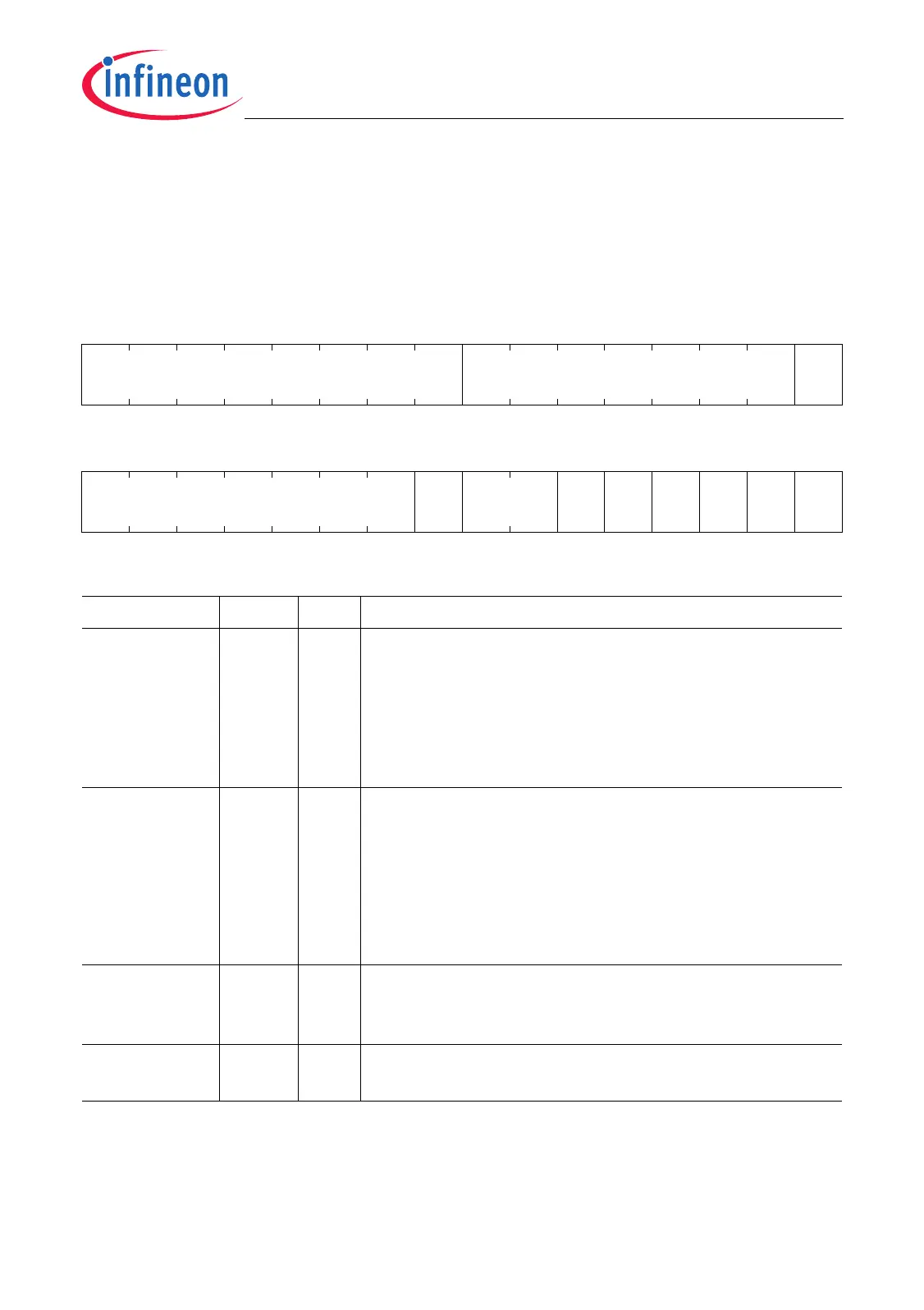

PCP_CS

PCP Control/Status Register (10

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ESR CWT CWE

rw rw rw

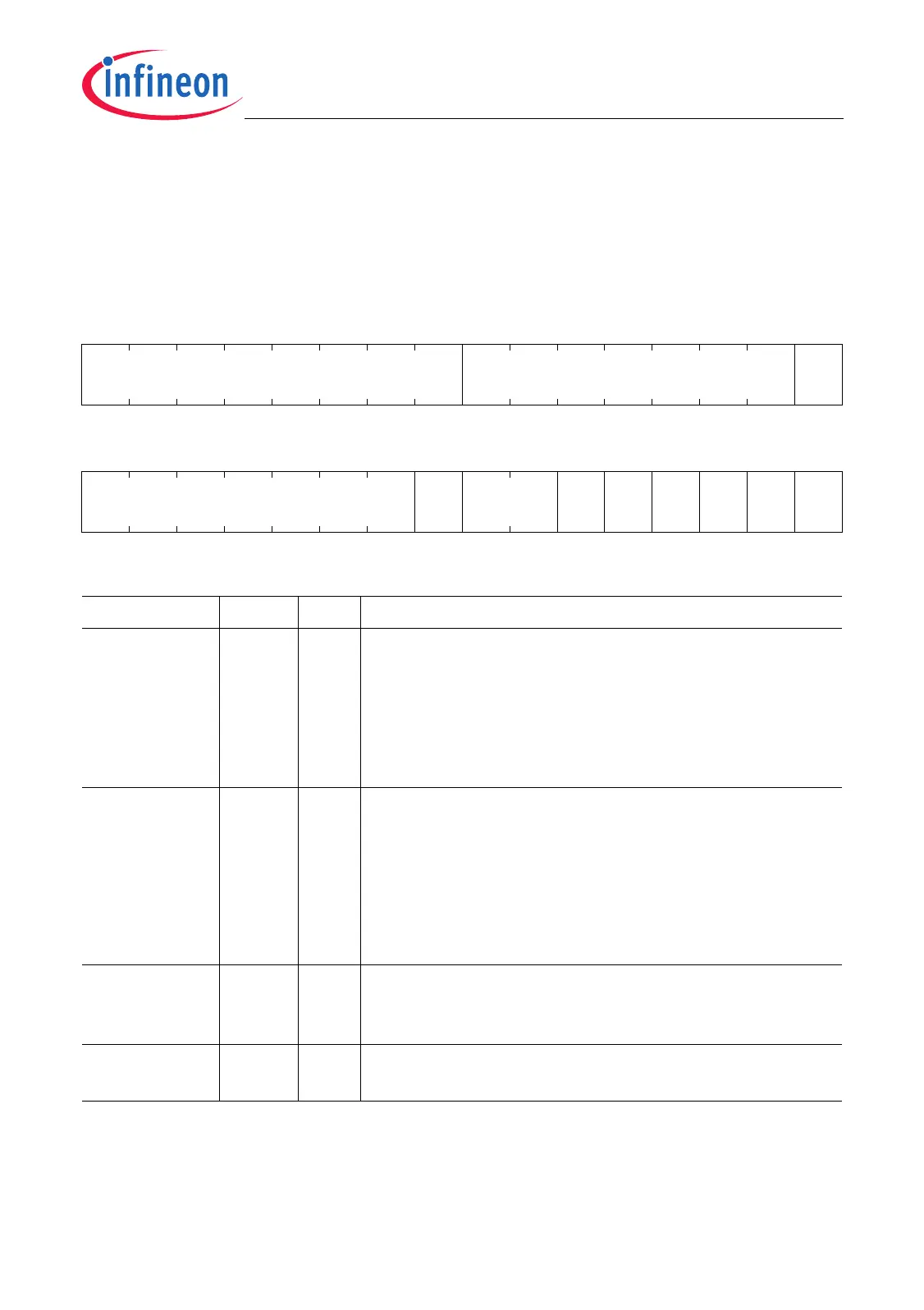

1514131211109876543210

PPS PPE CS EIE RCB 0 RS RST EN

rw rw rw rw rw r rh rwh rw

Field Bits Type Description

EN 0rwPCP Enable

0

B

PCP is disabled for operation (default)

1

B

PCP is enabled for operation

Note: This bit does not enable/disable clocks for

power saving. It stops the PCP from accepting

new service requests.

RST 1rwhPCP Reset Request

0

B

No PCP software reset operation is requested

1

B

A PCP software reset is requested. Halt any

operating channel. Reset all control registers to

default values. Reset PCP state to default value.

RST is always read as 0, but is written with 1 in order

to initiate a reset. See also Page 11-126.

RS 2rhPCP Run/Stop Status Flag

0

B

PCP is stopped or idle (default)

1

B

PCP is currently running

0 3rReserved

Read as 0; should be written with 0.

Loading...

Loading...