TC1796

System Units (Vol. 1 of 2)

System Timer

User’s Manual 15-5 V2.0, 2007-07

STM, V2.0

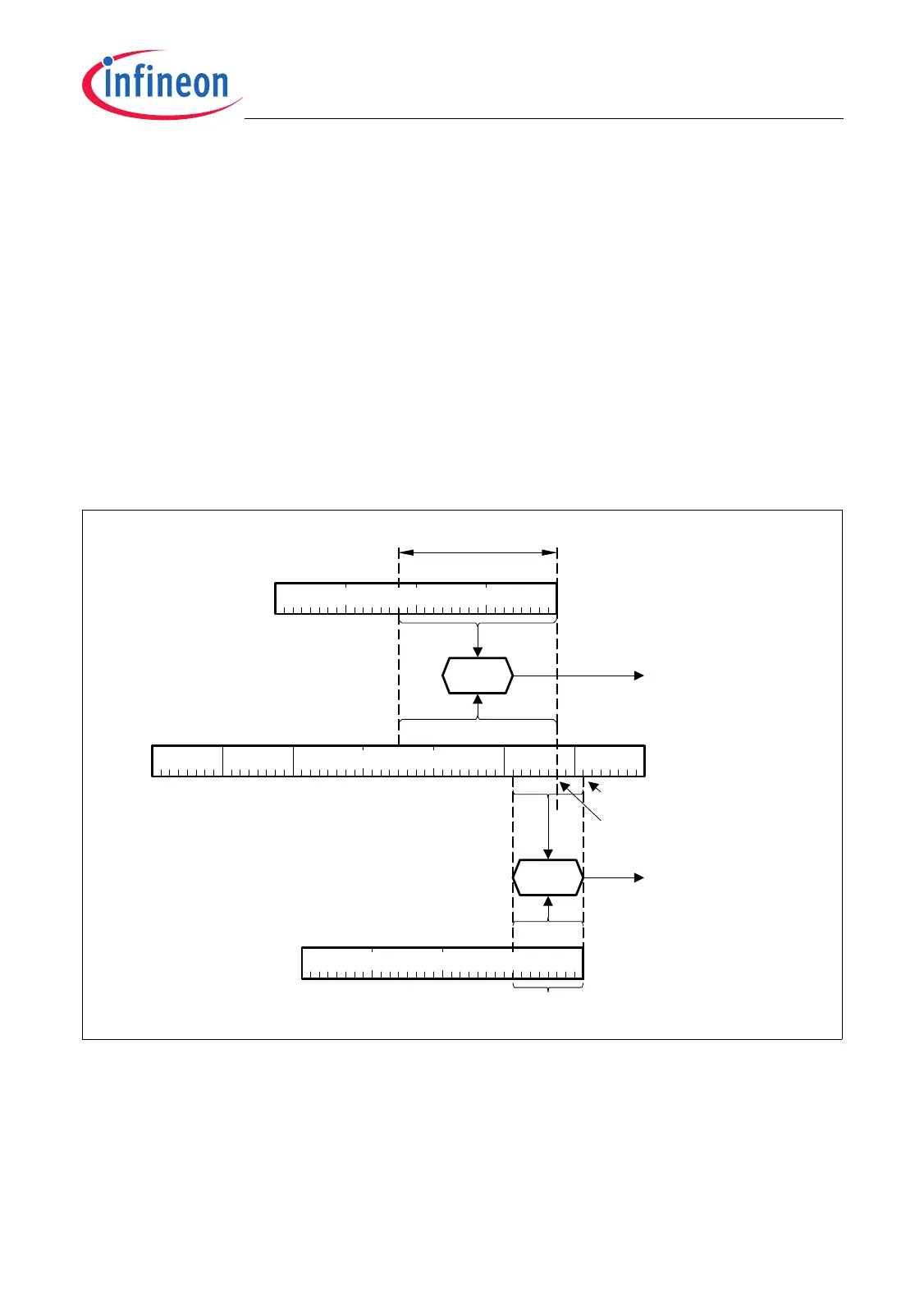

15.2.2 Compare Register Operation

The content of the 56-bit STM can be compared to the content of two compare values

stored in the STM_CMP0 and STM_CMP1 registers. Interrupts can be generated on a

compare match of the STM with the STM_CMP0 or STM_CMP1 registers.

Two parameters are programmable for the compare operation:

1. The width of the relevant bits in registers STM_CMP0/STM_CMP1 (compare width

MSIZEx) that is taken for the compare operation can be programmed from 1 to 32.

2. The first bit location in the 56-bit STM that is taken for the compare operation can be

programmed from 0 to 24.

These programming capabilities make compare functions very flexible. It even makes it

possible to detect bit transitions of a single bit n (n = 0 to 24) within the 56-bit STM by

setting MSIZE = 0 and MSTART = n.

Figure 15-2 Compare Mode Operation

Figure 15-2 shows an example of the compare operation. In this example the following

parameters are programmed:

• MSIZE0 = 10001

B

= 17

D

; MSTART0 = 01010

B

= 10

D

• MSIZE1 = 00111

B

= 7

D

; MSTART1 = 00111

B

= 7

D

55 47 39 31 23 15 7

56-Bit System Timer

31 23 15 7

Compare Register 0

Equal ?

Compare Match

with STM_CMP0

Register

MCA05747

MSIZE0

MSTART0

MSIZEx

MSTARTx

= 0-31

= 0-24

31 23 15 7

MSIZE1

Equal ?

Compare Match

with STM_CMP1

Register

MSTART1

Compare Register 1

STM_CMP1

STM_CMP0

Loading...

Loading...