TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual 22-136 V2.0, 2007-07

MultiCAN, V2.0

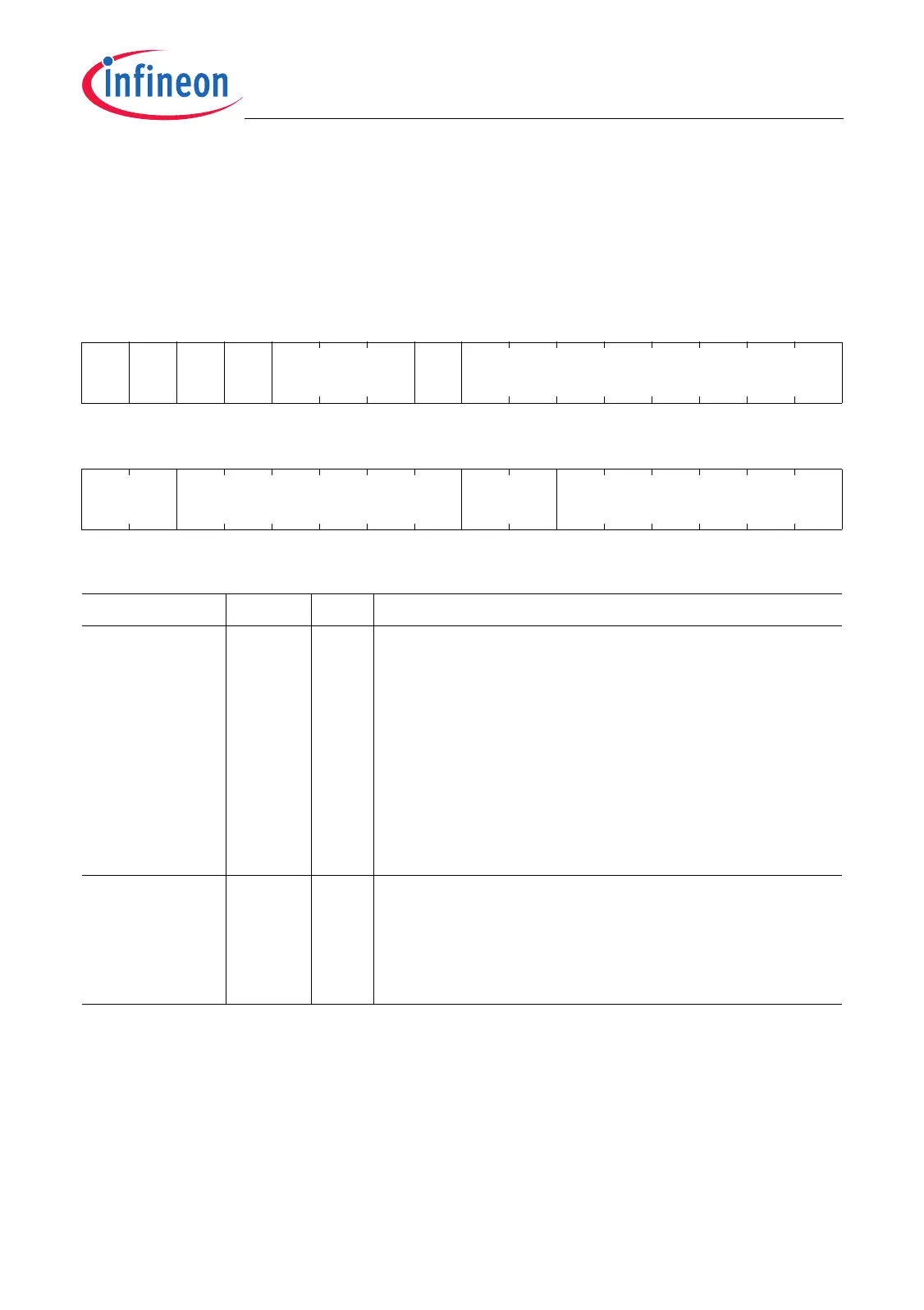

Receive Control Entry

The receive control entry is defined as follows:

RCE

Receive Control Entry

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0101 0

CH

EN

RCEMSGNR

rw rw rw rw r rw rw

1514131211109876543210

0 MCYCLE 0 CYCLE

rrw rrw

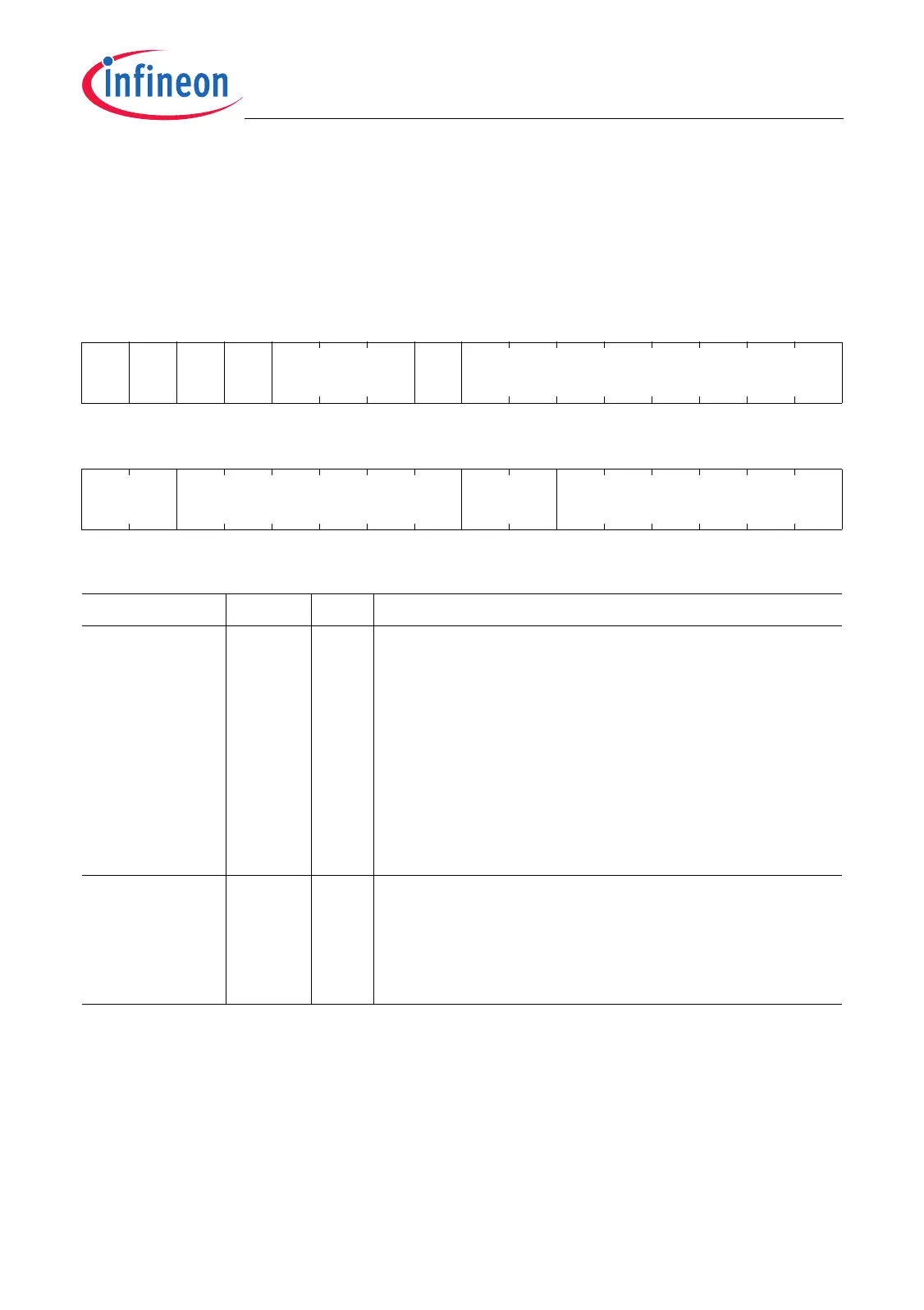

Field Bits Type Description

CYCLE [5:0] rw Basic Cycle Number

This bit field determines the number of the basic

cycle during which this receive control entry is valid.

The value of CYCLE is compared (bit-wise) to the

current value of the bit field CYCTMR.BCC. The

result is then masked with the value given by the bit

field MCYCLE in order to determine the repetition

rate for this scheduler entry inside the matrix cycle.

This bit field is equivalent to the corresponding part

of the MOAMRn.AM bit field (see Page 22-108).

MCYCLE [13:8] rw Mask for Cycle Comparison

This bit field determines the mask that is used to

determine the repetition rate for this scheduler entry.

This bit field is equivalent to the corresponding part

of the MOAMRn.AM bit field (see Page 22-108).

Loading...

Loading...