TC1796

System Units (Vol. 1 of 2)

Clock System and Control

User’s Manual 3-9 V2.0, 2007-07

Clock, V2.0

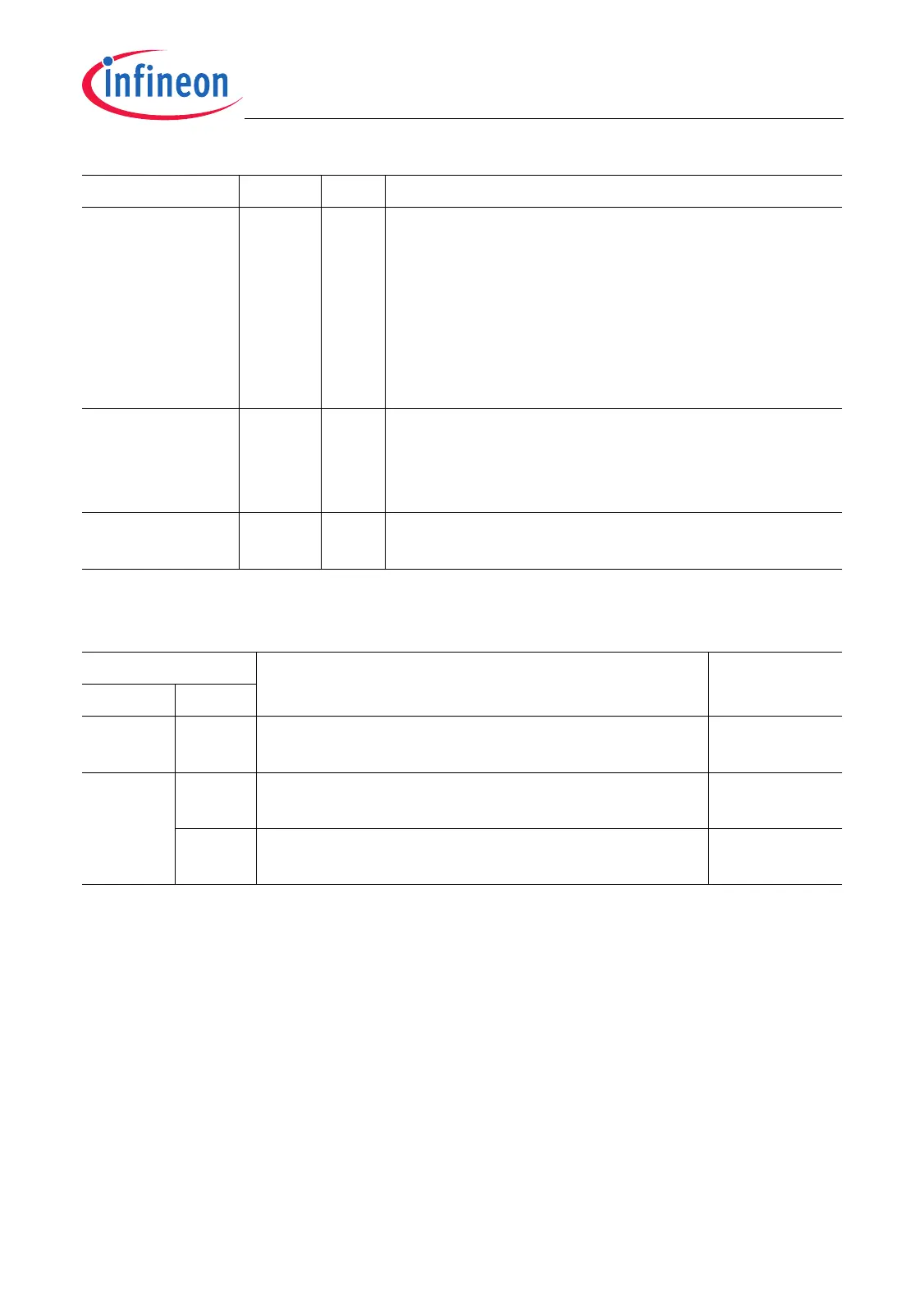

ORDRES 2rwhOscillator Run Detection Reset

This bit allows the oscillator run detection to start

during normal operating mode.

0

B

No operation

1

B

The oscillator run detection logic is reset and

restarted.

After ORDRES has been set, it becomes

automatically reset by hardware.

OGC 4rwOscillator Gain Control

This bit determines the main oscillator gain.

0

B

High gain is selected (default after reset).

1

B

Low gain is selected.

0 3,

[31:5]

r Reserved

Read as 0; should be written with 0.

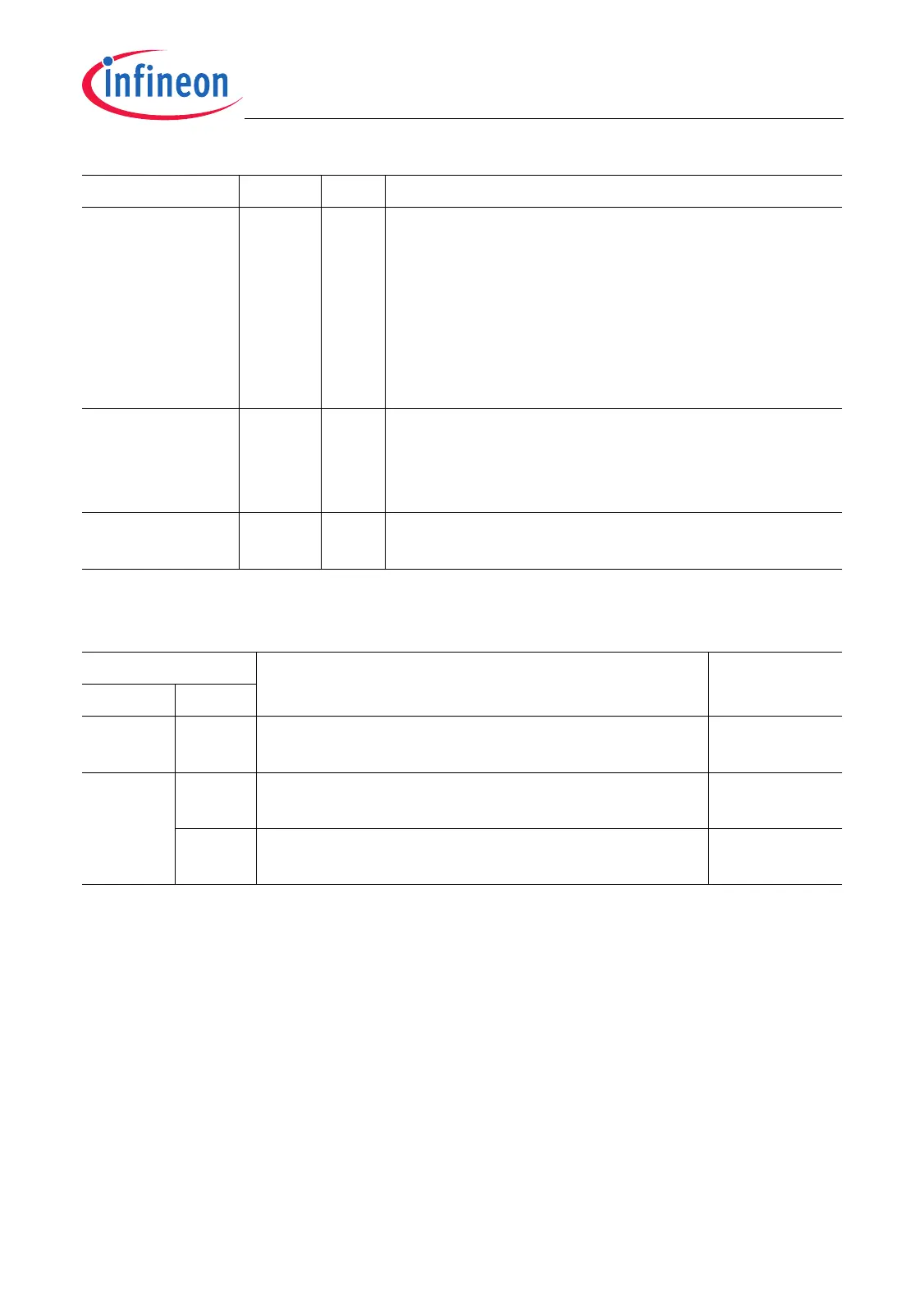

Table 3-1 Reset Values of Register OSC_CON

Condition Function Reset

Values

BYPASS TXD1A

0 X The system is driven by the PLL clock which is

derived from the oscillator clock.

0000 0000

H

1 0 The system is driven directly by the external clock

which is applied to XTAL1.

0000 0001

H

1 The system is driven by the crystal oscillator clock

or the external clock passed through the oscillator.

0000 0000

H

Field Bits Type Description

Loading...

Loading...