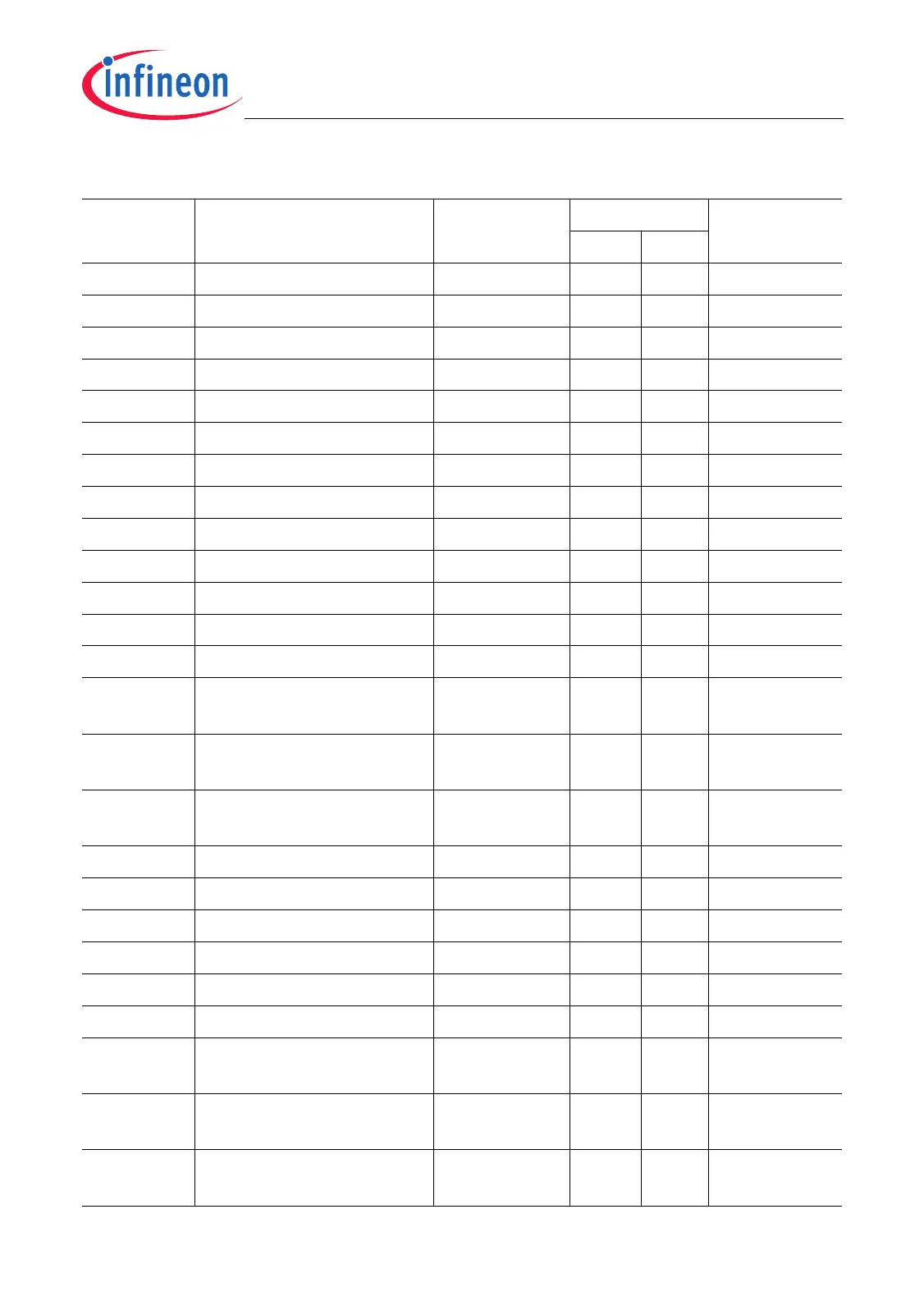

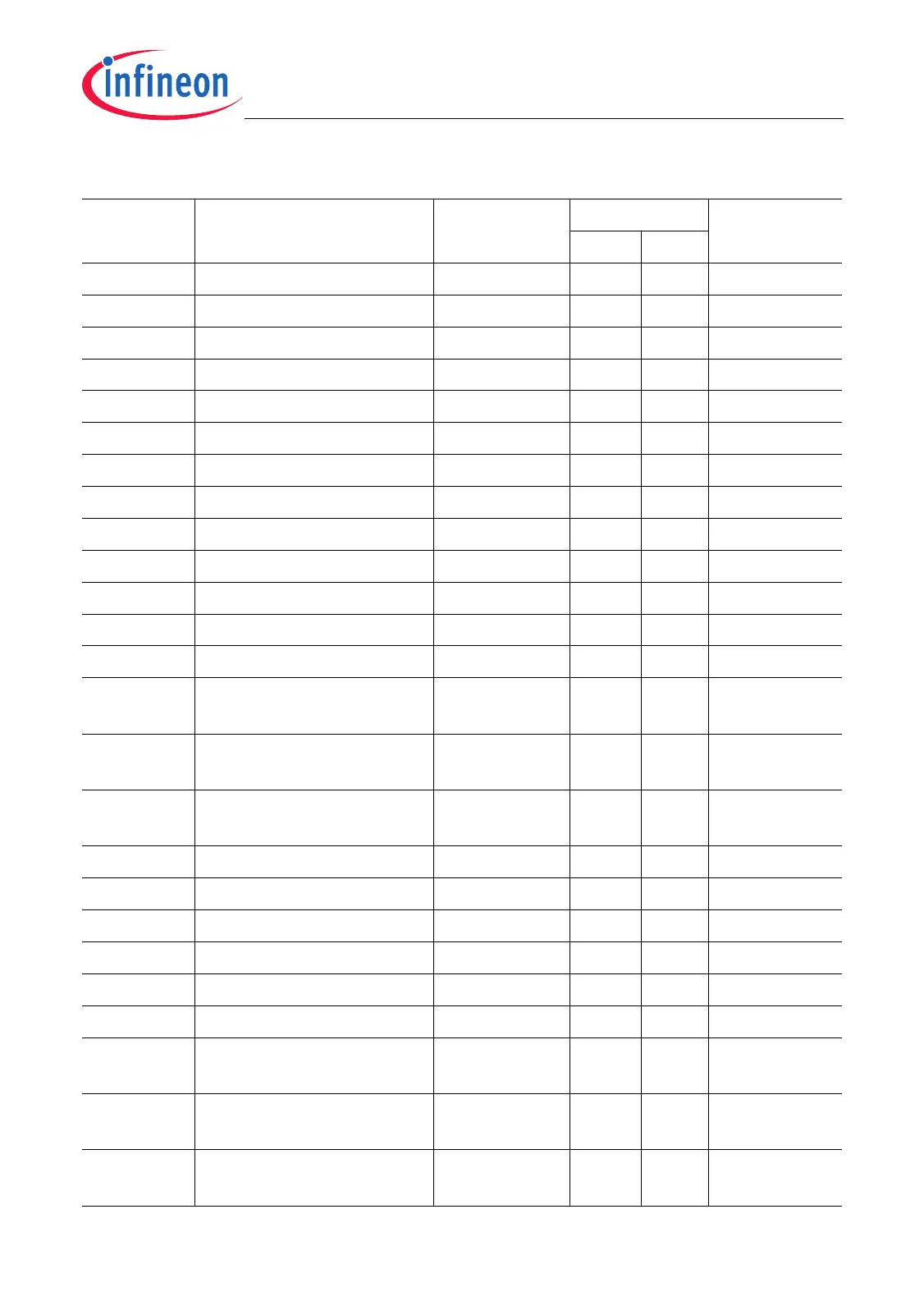

TC1796

System Units (Vol. 1 of 2)

Register Overview

User’s Manual 18-110 V2.0, 2007-07

Regs, V2.0

D3 Data Register 3 F7E1 FF0C

H

– – XXXX XXXX

H

D4 Data Register 4 F7E1 FF10

H

– – XXXX XXXX

H

D5 Data Register 5 F7E1 FF14

H

– – XXXX XXXX

H

D6 Data Register 6 F7E1 FF18

H

– – XXXX XXXX

H

D7 Data Register 7 F7E1 FF1C

H

– – XXXX XXXX

H

D8 Data Register 8 F7E1 FF20

H

– – XXXX XXXX

H

D9 Data Register 9 F7E1 FF24

H

– – XXXX XXXX

H

D10 Data Register 0 F7E1 FF28

H

– – XXXX XXXX

H

D11 Data Register 11 F7E1 FF2C

H

– – XXXX XXXX

H

D12 Data Register 12 F7E1 FF30

H

– – XXXX XXXX

H

D13 Data Register 13 F7E1 FF34

H

– – XXXX XXXX

H

D14 Data Register 14 F7E1 FF38

H

– – XXXX XXXX

H

D15 Data Register 15 F7E1 FF3C

H

– – XXXX XXXX

H

– Reserved F7E1 FF40

H

-

F7E1 FF7C

H

nE nE –

A0 Address Register 0

(Global Address Register)

F7E1 FF80

H

– – XXXX XXXX

H

A1 Address Register 1

(Global Address Register)

F7E1 FF84

H

– – XXXX XXXX

H

A2 Address Register 2 F7E1 FF88

H

– – XXXX XXXX

H

A3 Address Register 3 F7E1 FF8C

H

– – XXXX XXXX

H

A4 Address Register 4 F7E1 FF90

H

– – XXXX XXXX

H

A5 Address Register 5 F7E1 FF94

H

– – XXXX XXXX

H

A6 Address Register 6 F7E1 FF98

H

– – XXXX XXXX

H

A7 Address Register 7 F7E1 FF9C

H

– – XXXX XXXX

H

A8 Address Register 8

(Global Address Register)

F7E1 FFA0

H

– – XXXX XXXX

H

A9 Address Register 9

(Global Address Register)

F7E1 FFA4

H

– – XXXX XXXX

H

A10 Address Register 10

(Stack Pointer)

F7E1 FFA8

H

– – XXXX XXXX

H

Table 18-33 Address Map of CPU Core SFRs & GPRs (cont’d)

Short

Name

Description Address Access Mode Reset Value

Read Write

Loading...

Loading...