TC1796

Peripheral Units (Vol. 2 of 2)

Synchronous Serial Interface (SSC)

User’s Manual 20-19 V2.0, 2007-07

SSC, V2.1

In the TC1796, the module clock f

SSC

is generated outside the SSC module kernel.

Therefore, for baud rate calculations the dependencies of f

SSC

from f

SYS

must be taken

into account. Section 20.3.2.1 on Page 20-48 describes these dependencies in detail.

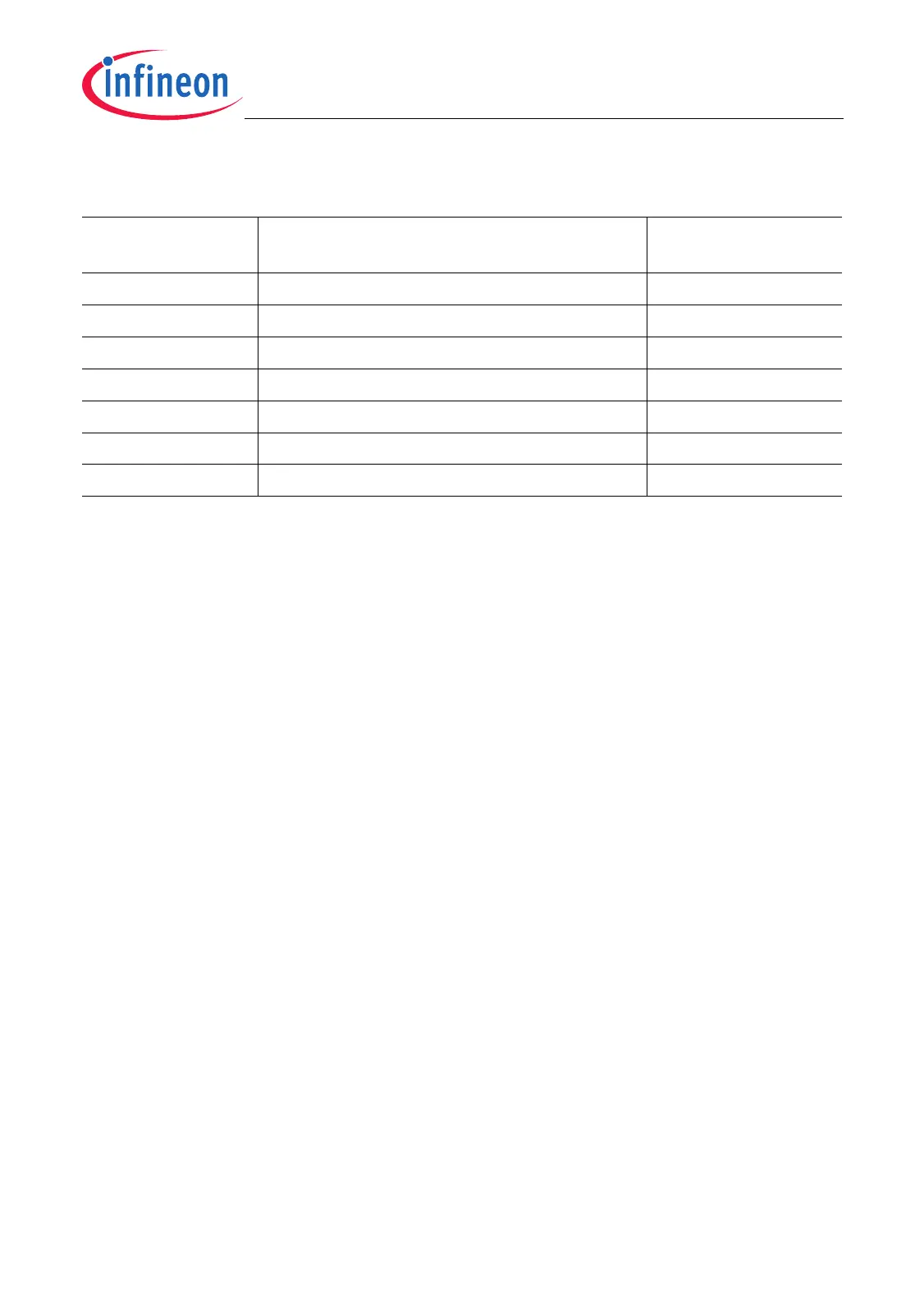

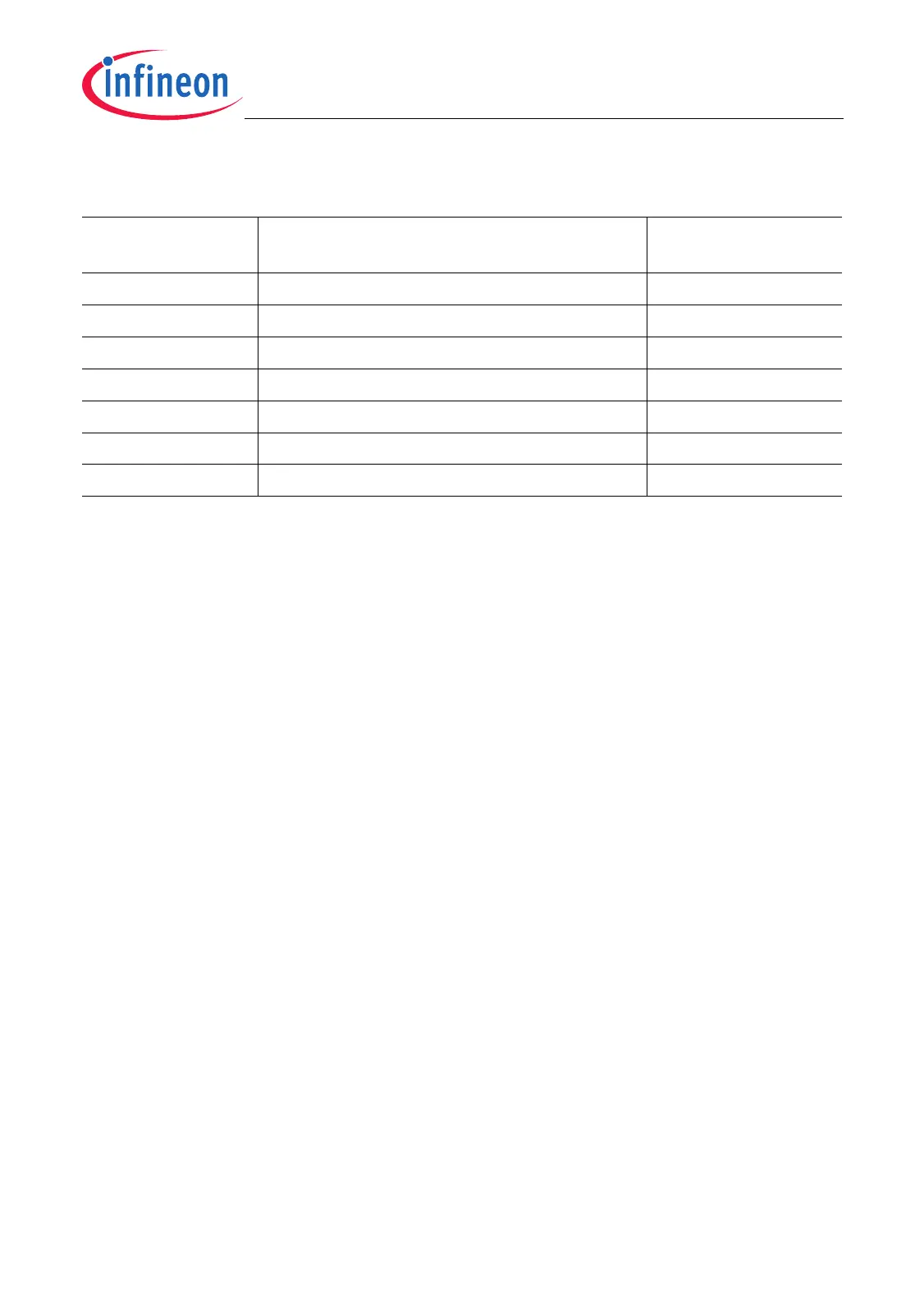

Table 20-1 Typical Baud Rates of the SSC (f

SSC

= 75 MHz)

Reload Value

BR_VALUE

Baud Rate (= f

SCLK

) Deviation

0000

H

37.5 Mbit/s (only in Master Mode) 0.0%

0001

H

18.75 Mbit/s 0.0%

0025

H

1 Mbit/s -1.3%

0176

H

100 kbit/s 0.0%

0EA5

H

10 kbit/s 0.0%

9276

H

1 kbit/s 0.0%

FFFF

H

572.2 bit/s 0.0%

Loading...

Loading...