TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual 22-71 V2.0, 2007-07

MultiCAN, V2.0

Each Message Pending Register has a Message Index Register MSIDk associated with

it. The Message Index Register MSIDk shows the active (set) pending bit with lowest bit

position within groups of pending bits.

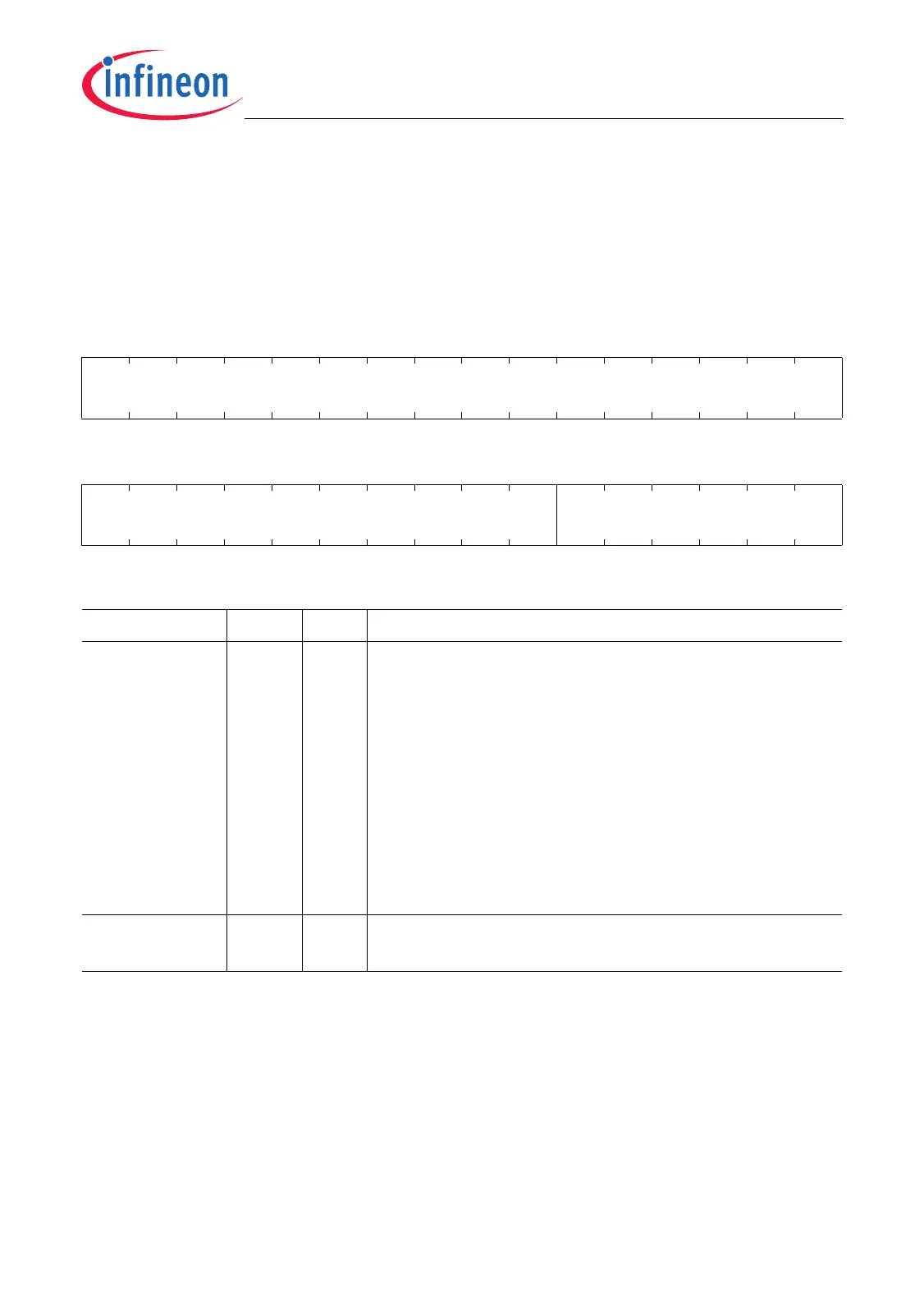

MSIDk (k = 0-7)

Message Index Register k (140

H

+k*4

H

) Reset Value: 0000 0020

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0INDEX

rrh

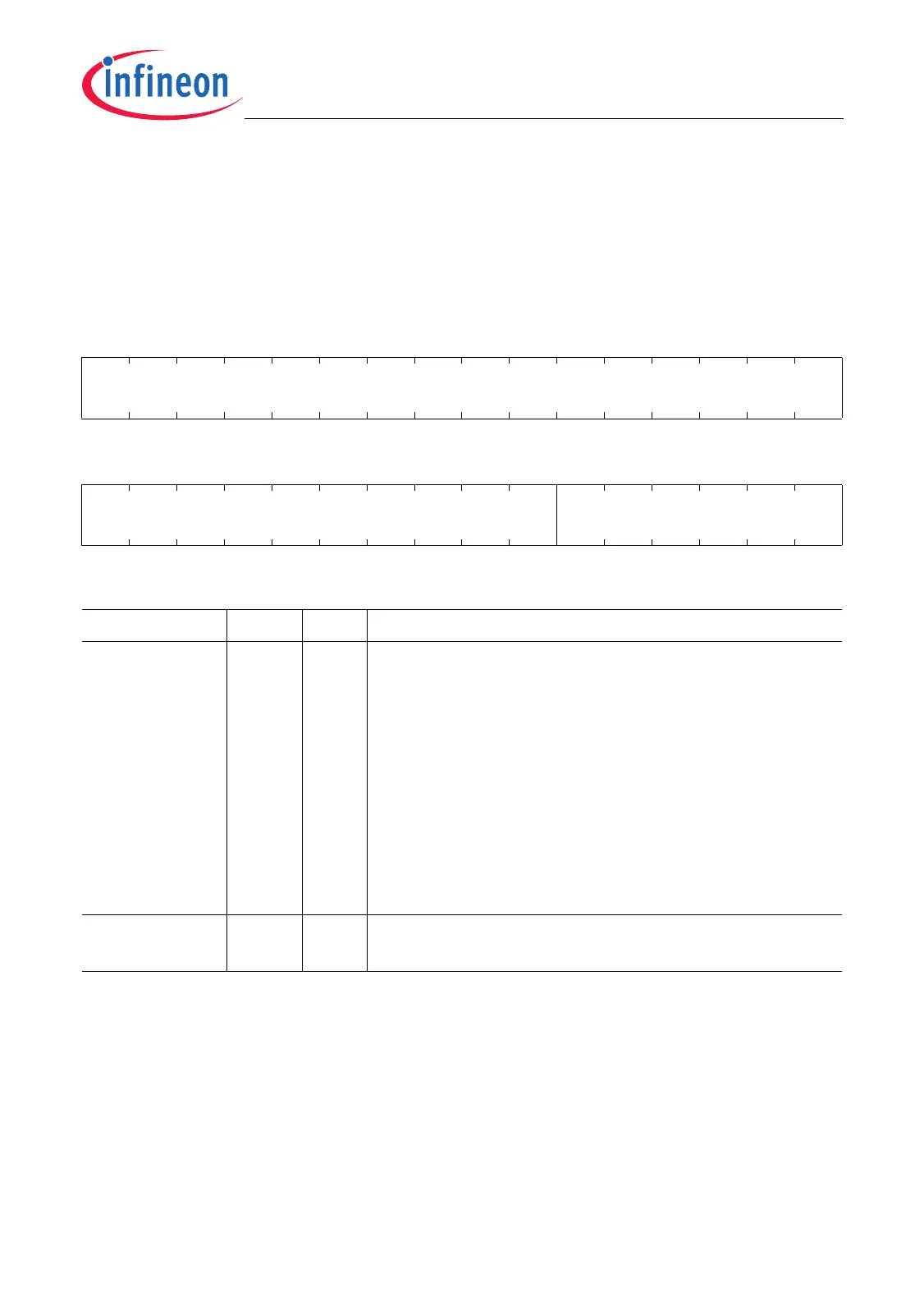

Field Bits Type Description

INDEX [5:0] rh Message Pending Index

The value of INDEX is given by the bit position i of the

pending bit of MSPNDk with the following properties:

1. MSPNDk[i] & IM[i] = 1

2. i = 0 or MSPNDk[i-1:0] & IM[i-1:0] = 0

If no bit of MSPNDk satisfies these conditions then

INDEX reads 100000

B

.

Thus INDEX shows the position of the first pending bit

of MSPNDk, in which only those bits of MSPNDk that

are selected in the Message Index Mask Register are

taken into account.

0 [31:6] r Reserved

Read as 0; should be written with 0.

Loading...

Loading...