TC1796

Peripheral Units (Vol. 2 of 2)

Micro Link Interface (MLI)

User’s Manual 23-27 V2.0, 2007-07

MLI, V2.0

• Bit field TPxBAR.ADDR (28 most significant base address bits) is loaded into bit field

TCBAR.ADDR.

• Status bit field TRSTATR.PN is updated with the pipe number x (for example x = 2

when TP2BAR has been written).

• Status flag TRSTATR.BAV (base address valid) becomes set.

• The transmission of a Copy Base Address Frame with the two buffered parameters

TCBAR.ADDR and TPxSTATR.BS is started for pipe x (if the corresponding pipe is

idle and TREADY = 1).

• Status flag TRSTATR.BAV (in the transmitting controller) is cleared after the Copy

Base Address Frame has been finished and correctly acknowledged by the MLI

receiver of the receiving controller.

• MLI event status flag TISR.NFSIx (Normal Frame Sent event in pipe x) is set and a

service request output is activated if enabled by TIER.NFSIEx = 1.

Note: After the transfer of a Copy Base Address Frame the optimized mode will be

suppressed automatically by hardware for the next two data frames. This ensures

a correct offset prediction afterwards.

Receiving Controller

When a Copy Base Address Frame for pipe x has been received correctly and

acknowledged, the following actions are executed in the MLI receiver.

• The received 28 most significant address bits are written into the receiver pipe x base

address register bit field RPxBAR.ADDR. This bit field determines the base address

of the pipe x Remote Window.

• The received 4-bit coded buffer size is stored in the receiver pipe x status register bit

field RPxSTATR.BS. This bit field determines the number of variable address bits for

the offset (determining the size) of the pipe x Remote Window.

• The information about the received frame type (= 00

B

for Copy Base Address Frame)

is written into the receiver control register bit field RCR.TF.

• MLI event status flag RISR.NFRI (Normal Frame Received event) is set and a service

request output is activated if enabled by RIER.NFRIE = 01

B

or 10

B

.

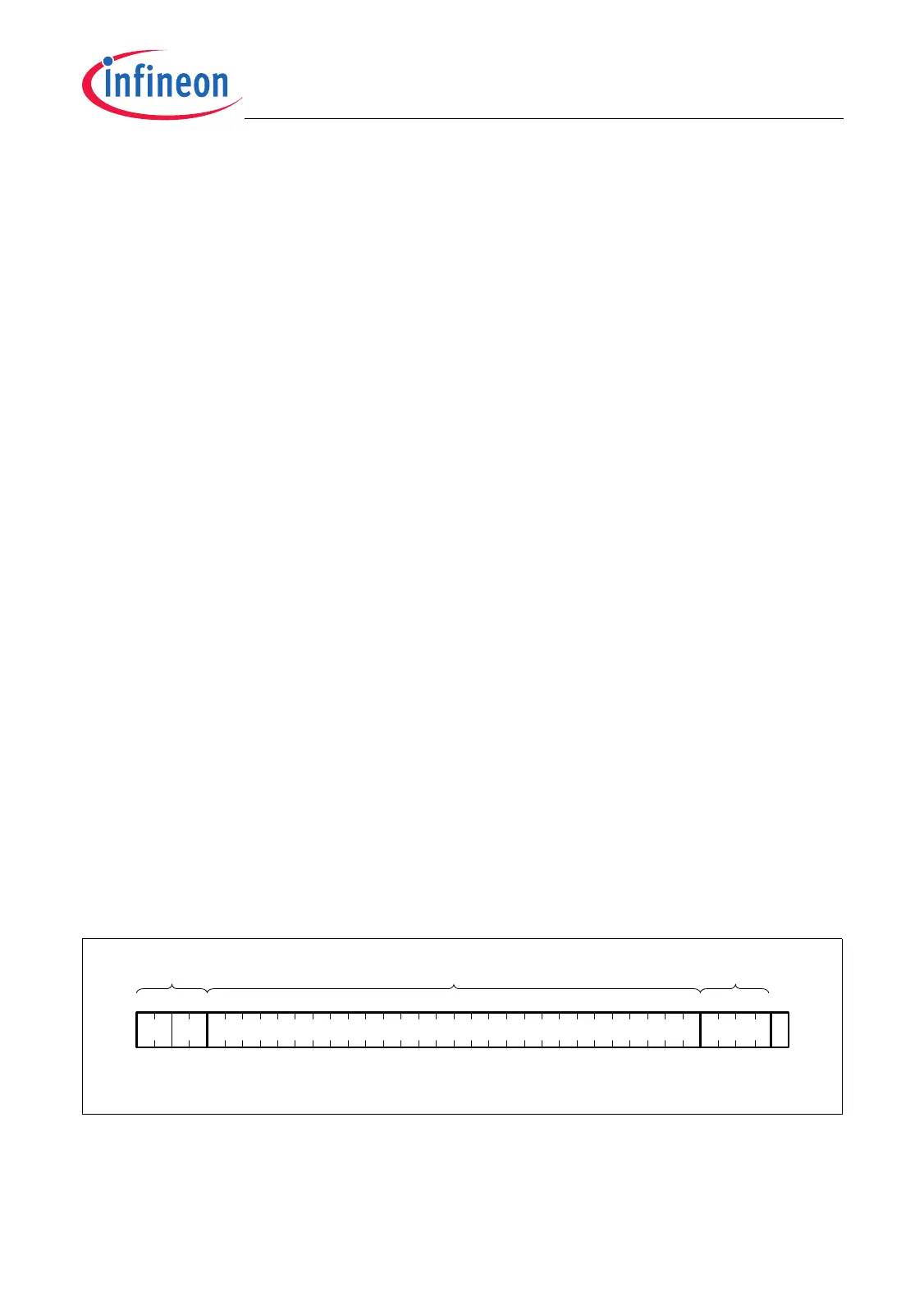

Figure 23-21 Copy Base Address Frame

MCA05879

x

P

Base Address (28-bit)0

024

BS

32 3631 31 35

0

x = Pipe Number

TCBAR.ADDR TPxSTATR.BSHeader

Loading...

Loading...