TC1796

Peripheral Units (Vol. 2 of 2)

Fast Analog-to-Digital Converter (FADC)

User’s Manual 26-37 V2.0, 2007-07

FADC, V2.0

The Global Control Register GCR contains bits used to clear the Channel Timers, the

filters and to control global FADC settings.

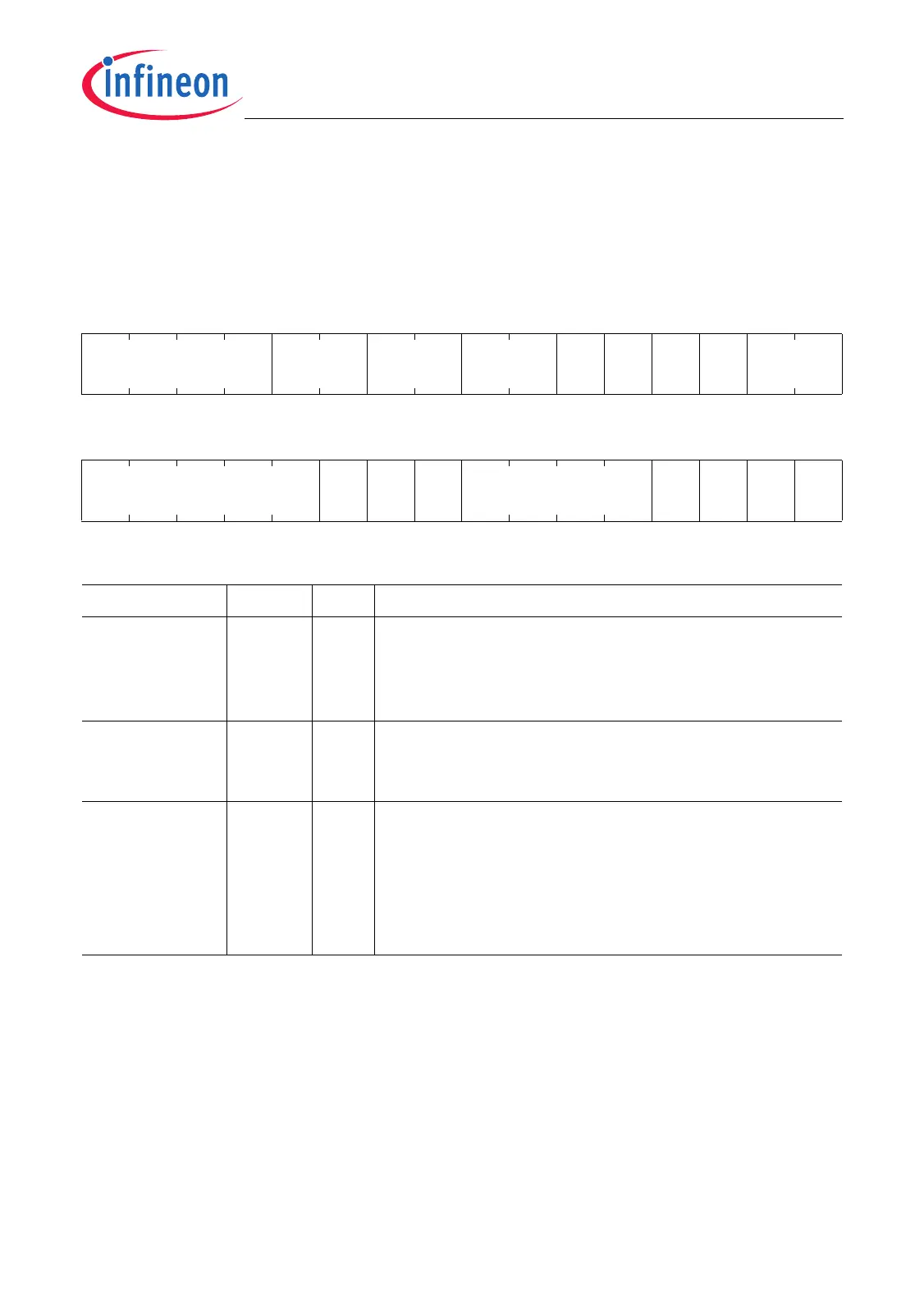

GCR

Global Control Register (1C

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0 CALCH CALMODE 0

AN

ON

MUX

TM

RES

WEN

DPA

EN

CRPRIO

r rw rw r rw rw rw rw rwh

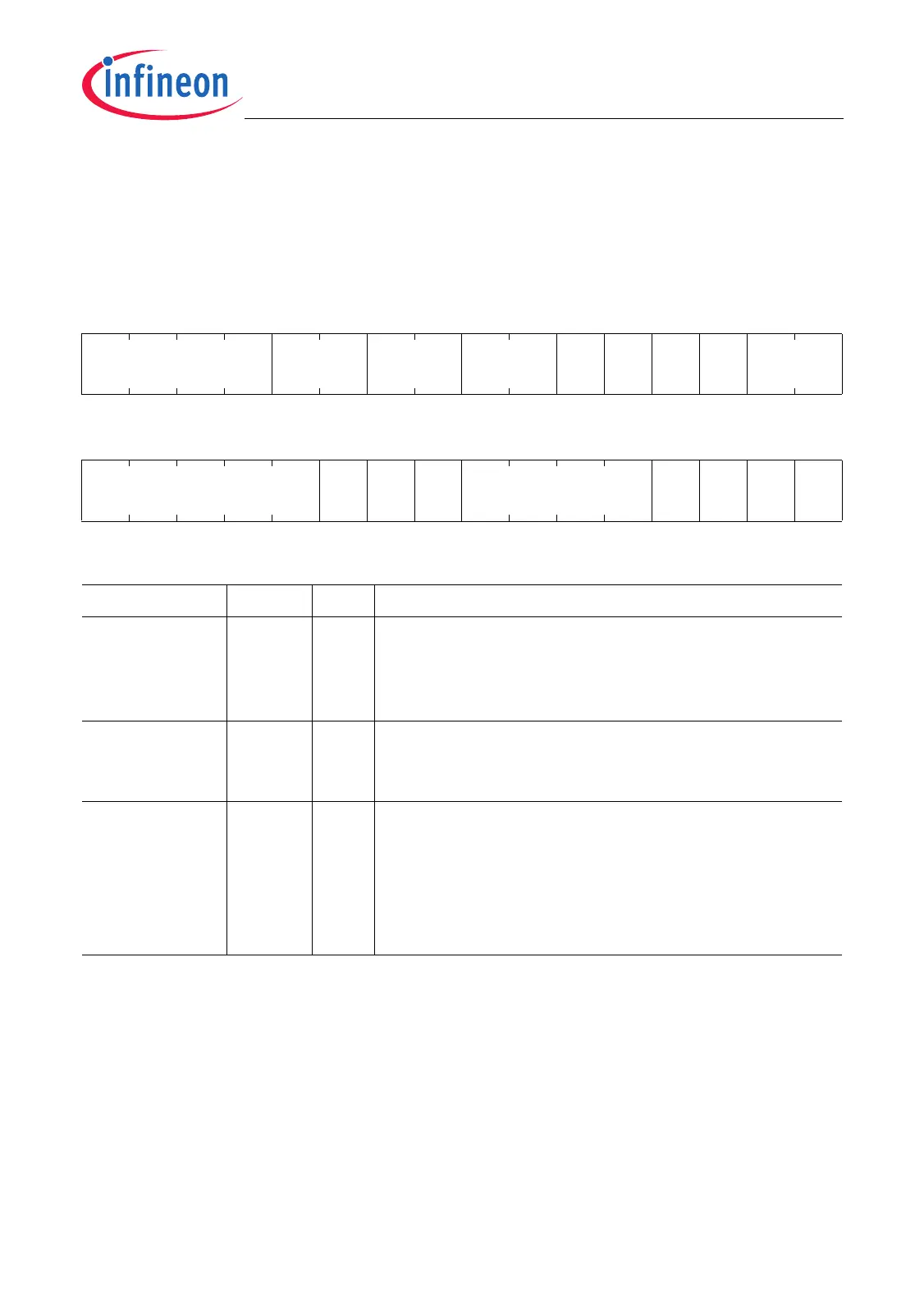

1514131211109876543210

0

RST

F1

RST

F0

RCD 0

RCT

3

RCT

2

RCT

1

RCT

0

r www r wwww

Field Bits Type Description

RCTx

(x = 0-3)

xwReload Channel Timer

0

B

Channel x Timer will not be changed.

1

B

Channel x Timer will be loaded with its reload

value.

RCD 8wReset Common Divider

0

B

The common divider will not be changed.

1

B

The common divider will be cleared.

RSTFn

(n = 0-1)

9 + n w Reset Filter n

0

B

The contents of filter n will not be changed.

1

B

The contents of filter n will be cleared.

The values of the bits in the filter registers will

be cleared, except bit field CRRn.AC which is

loaded with the value of FCRn.ADDL.

Loading...

Loading...