TC1796

System Units (Vol. 1 of 2)

On-Chip System Buses and Bus Bridges

User’s Manual 6-39 V2.0, 2007-07

Buses, V2.0

SBCU_ECON

SBCU Error Control Capture Register (20

H

) Reset Value: 0000 0000

H

RBCU_ECON

RBCU Error Control Capture Register (20

H

) Reset Value: 0000 0000

H

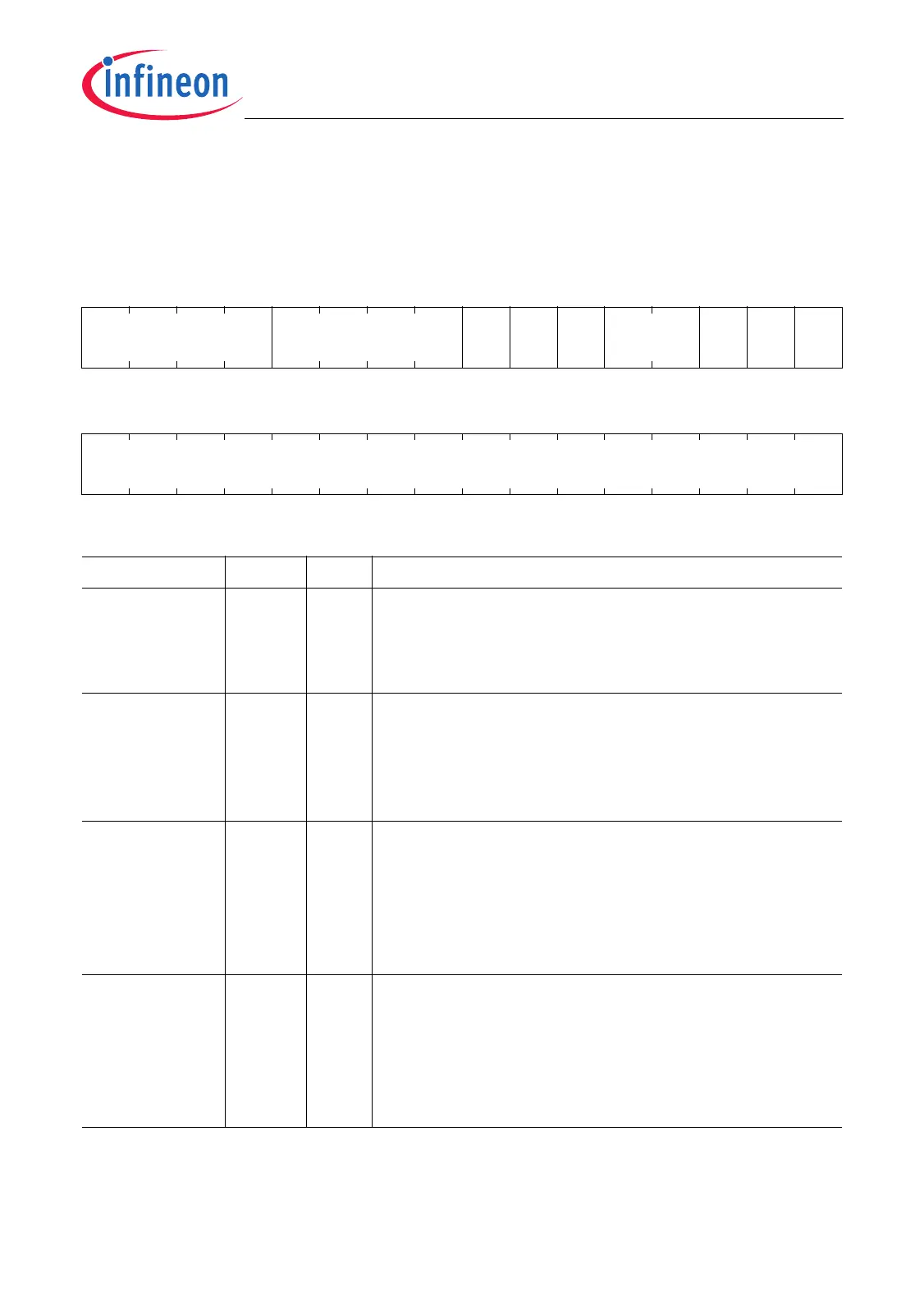

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

OPC TAG RDN WRN SVM ACK ABT RDY

T

OUT

rwh rwh rwh rwh rwh rwh rwh rwh rwh

1514131211109876543210

ERRCNT

rwh

Field Bits Type Description

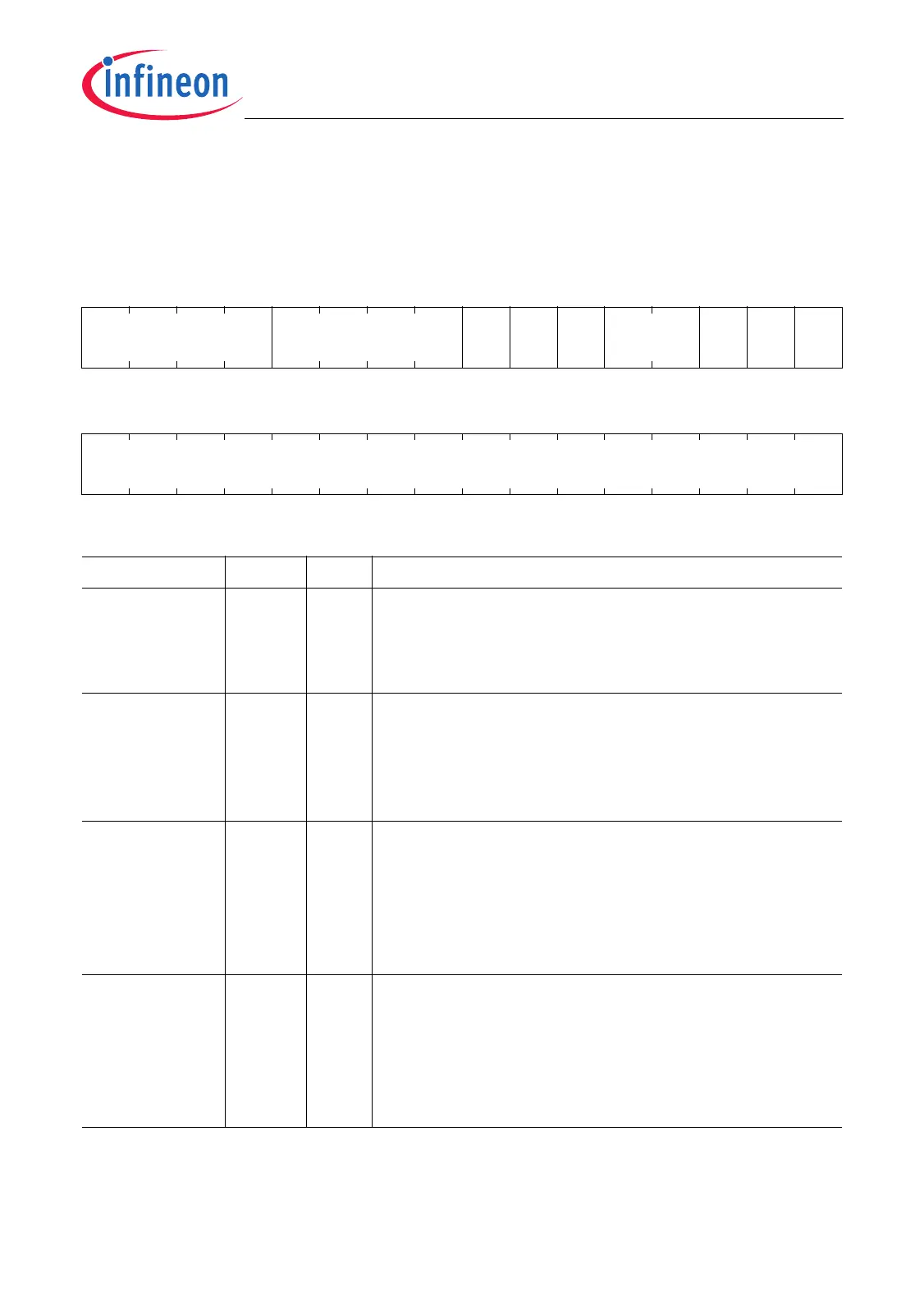

ERRCNT [15:0] rwh FPI Bus Error Counter

ERRCNT is incremented on every occurrence of an

FPI Bus error. ERRCNT is reset to 0000

H

after the

ECON register is read.

1)

TOUT 16 rwh State of FPI Bus Time-Out Signal

This bit indicates the state of the time-out signal at an

FBI Bus error.

0

B

No time-out occurred.

1

B

Time-out has occurred.

RDY 17 rwh State of FPI Bus Ready Signal

This bit indicates the state of the ready signal at an

FBI Bus error.

0

B

Wait state(s) have been inserted. Ready signal

was active.

1

B

Ready signal was inactive.

ABT 18 rwh State of FPI Bus Abort Signal

This bit indicates the state of the abort signal at an

FBI Bus error.

0

B

Master has aborted an FPI Bus transfer. Abort

signal was active.

1

B

Abort signal was inactive.

Loading...

Loading...